Test Tesisleri için Kapsamlı Kılavuz: Dijital Sistem Doğrulaması için Araçlar ve Teknikler

Bu kılavuz, girişleri test etmek ve çıktıları doğrulamak için koşulları simüle eden yazılım doğrulaması için anahtar bir araç olan Testbenches'i araştırıyor.Testbenches, geliştirmenin erken dönemlerinde hataların belirlenmesinde, yazılım güvenilirliğini artırmada rol oynar.Pratik örnekler ve içgörülerle bu makale, güçlü, verimli dijital sistemler oluşturmada kullanımlarını, tekniklerini ve önemlerini vurgulamaktadır.Katalog

Dijital Sistem Validasyonundaki Test Tesisatlarının Rolü

Testbench, dijital sistem doğrulama sürecinde bir bileşendir.Yalnızca girişler üretmek ve çıktıları doğrulamak için bir araç değildir, dijital sistemlerin sahaya yerleştirilmeden önce güvenilirliğini, işlevselliğini ve davranışını değerlendirmek için koşulları simüle eden kapsamlı bir çerçeve görevi görür.Çok çeşitli girdi senaryolarına sahip stres testi sistemlerine kontrollü ortamlar oluşturarak, test tezgahları, sistem üretilmeden çok önce, geliştirme yaşam döngüsünün başlarında potansiyel tasarım kusurlarını belirlemenize yardımcı olur.Maliyetli hataların azaltılması, performans özelliklerine uyum sağlamak ve genel sistem güvenilirliğini artırmak için hataların ve güvenlik açıklarının bu erken tespiti gereklidir.

Sistemin tepkilerinin doğruluğunu doğrulamanın yanı sıra, test tezgahları, kenar vakalarını, zamanlama sorunlarını ve hata işleme mekanizmalarının değerlendirilmesinde rol oynar ve sistemin aşırı veya beklenmedik koşullar altında bile doğru çalışabilmesini sağlar.Otomatik test ve simülasyon yoluyla, test tezgahları, manuel müdahale olmadan yinelemeli testlere izin vererek daha yüksek yazılım kalitesine, gelişmiş performans ve daha kısa geliştirme döngülerine katkıda bulunur.Dijital sistemlerin sağlamlığını ve güvenilirliğini sağlayarak, dağıtımdan sonra meydana gelebilecek arızalara karşı bir koruma görevi görürler.

Bir test bankasının temel bileşenleri ve işlevleri

Test bankalarının nasıl çalıştığını daha iyi anlamak için, bunları etkili kılan bileşenleri keşfetmek önemlidir.İyi hazırlanmış bir Testbench, iki temel görevi yöneterek çalışır: girişler (uyaranlar) üretme ve çıktıları doğrulamak.Her bileşeni ayrıntılı olarak inceleyelim.

Uyarıcı üretim

Uyarıcı üretimi, bir dijital sistemin davranışını test etmek için koşulları simüle eden bir dizi giriş sinyali oluşturmayı içerir.Sistemin pratikte karşılaşabileceği çeşitli senaryolara maruz kalmasını sağlamak için bu girdilerin hem kesin hem de gerçekçi olması gerekir.Örnek olarak temel bir RAM modülünü düşünün.Testbench, modüle belirli girişler sağlamalı ve beklendiği gibi davrandığından emin olmak için çıktılarını gözlemlemelidir.Bir RAM modülü için anahtar girişler tipik olarak şunları içerir:

• CLK (Saat): Sistemin zamanlamasını yönlendirir.

• ADDR (Adres): Hangi veri konumuna erişileceğini belirtir.

• wen (yazma etkinliği): Verilerin belleğe yazılıp yazılmadığını kontrol eder.

• Veri: Modüle yazılan gerçek bilgiler.

Verias olarak bilinen çıkış, modülün dahili işlemlerinin sonucunu temsil eder.Bu girdilerin nasıl teslim edildiğini dikkatle komut dosyası yazarak ve verioutu izleyerek, sistemin farklı senaryolar altında doğru bir şekilde performans gösterdiğini doğrulayabilirsiniz.Uyarıcı üretimini bir laboratuvarda bir test senaryosu oluşturma olarak düşünün.Bilim adamlarının kimyasal reaksiyonları gözlemlemek için koşulları dikkatlice kontrol ettiği gibi, dijital tasarımcılar bir sistemin nasıl tepki verdiğini gözlemlemek için kesin girdiler üretiyorlar.

Çıktı Doğrulama

Çıktı doğrulaması, sistemin gerçek çıktılarının beklenen sonuçlarla eşleştiğini kontrol etme işlemidir.Bu adım, daha büyük sorunlara dönüşmeden önce hataları yakalamada kritik öneme sahiptir.Diğerleri, sistemin amaçlanan işlevselliğini karşıladığını ve çeşitli koşullar altında tutarlı bir şekilde performans gösterdiğini doğrulamak için çıktı doğrulamasını kullanır.Çıktı doğrulaması hem otomatik hem de manuel kontrolleri içerir.Örneğin:

• Otomatik doğrulama araçları: ModelSim ve Quartus gibi araçlar, sistem çıkışlarının beklenen sonuçlarla karşılaştırıldığı otomatik testlere izin verir.Bu doğrulama işlemini hızlandırır ve hatayı azaltır.

• Manuel doğrulama (isteğe bağlı): Daha karmaşık senaryolar için, belirli kenar durumlarının kapsanmasını sağlamak için manuel kontroller gerekebilir.

Testbench uygulaması için araçlar ve teknikler

Quartus: Görsel giriş/çıkış simülasyonu

Quartus, girişleri görsel olarak düzenleyen ve çıkışları gözlemleyen grafik bir arayüz sağlar.Bu yöntem yeni başlayanlar veya daha uygulamalı, görsel bir yaklaşım gerektiren sistemler için faydalı olabilir.Bir simülasyonla grafiksel bir ortam yoluyla etkileşime girmeye izin vererek Quartus, girişler ve çıkışlar arasındaki ilişkiyi tanımlamaya yardımcı olur, bu da bir dijital sistemin zamanla nasıl davrandığını anlamayı kolaylaştırır.Quartus'un temel güçlü yanlarından biri, yeni başlayanlar için ideal olmasıdır.Sezgisel, görsel arayüzü, girişlerin kapsamlı komut dosyası veya programlama bilgisine ihtiyaç duymadan çıktıları nasıl etkilediğini görmek için basit bir yol sağlar.Sunduğu geri bildirim, devrelerin davranışını daha kolay kavramaya yardımcı olur ve bu da onu dijital sistem tasarımına yeni olanlar için yararlı bir araç haline getirir.Ancak, Quartus'un sınırlamaları vardır.Quartus'ta simülasyonların ayarlanması, özellikle daha karmaşık tasarımlar için zaman alıcı olabilir.Araç, daha fazla özelleştirme ve otomasyon seçenekleri sunabilen komut dosyası tabanlı simülasyon araçlarına kıyasla daha az esnektir.Büyük ölçekli veya son derece ayrıntılı sistemler üzerinde çalışmak için, bu esneklik eksikliği bir zorluk yaratabilir.

ModelSim: Komut dosyası kullanarak metin tabanlı simülasyon

ModelSim, komut dosyası yoluyla metin tabanlı girdiyi önceliklendirerek simülasyona farklı bir yaklaşım benimser.Girişleri ve çıkışları görsel olarak düzenlemek yerine verilog (.v) veya VHDL (.vhd) komut dosyalarını kullanarak test senaryoları oluşturun.Bu yöntem daha fazla hassasiyet ve kontrol sağlar.Grafik bir arayüze güvenmek yerine, sistemin ayrıntılı komut dosyaları aracılığıyla nasıl test edilmesi gerektiğini tanımlayarak simülasyon işleminde daha fazla özelleştirme ve otomasyon sağlayarak tanımlarsınız.Modellerin temel güçlü yönlerinden biri sunduğu esnekliktir.Komut dosyalarını kullanarak, test senaryoları üzerinde daha fazla kontrole sahip olursunuz, bu da karmaşık ve kesin simülasyonlar oluşturmalarını sağlar.Bir tasarımcı sözdizimi ve iş akışına aşina olduğunda, simülasyonlar ayarlama Quartus gibi grafik araçları kullanmaya kıyasla çok daha hızlı olabilir.Komut dosyalarını yeniden kullanma ve değiştirme yeteneği, özellikle daha büyük projelerde verimliliğine de katkıda bulunur.Bununla birlikte, ModelSim'in metin tabanlı yaklaşımı belirli sınırlamalarla birlikte gelir.Donanım açıklama dillerine aşina olmayan yeni başlayanlar için bir zorluk oluşturabilecek Verilog veya VHDL sözdiziminin sağlam bir şekilde anlaşılmasını gerektirir.Sonuç olarak, ModelSim daha görsel simülasyon araçlarına kıyasla daha dik bir öğrenme eğrisine sahiptir.Yeni kullanıcılar başlamakta zorlanabilir, ancak pratikle, komut dosyası tarafından sunulan hassasiyet ve esneklik değerli bir varlık haline gelebilir.

Doğrulamada köprü teorisi ve uygulama

Testbenches, bir dijital sistemin kenar durumları ve beklenmedik girdiler de dahil olmak üzere çeşitli koşullar altında nasıl davranacağını simüle ederek teorik tasarımlar ve uygulamalar arasında bir köprü görevi görür.Dijital tasarımda, bir sistemin yalnızca teorik modellere dayanarak pratikte nasıl performans göstereceğini tahmin etmek genellikle zordur.Soyut tasarım kavramlarının ötesine geçmenize ve bir sistemin davranışını kontrollü, simüle edilmiş bir ortamda değerlendirmenize izin vererek bu boşluğu kapatır.Simülasyon araçlarını Testbenches'de kullanmanın temel avantajlarından biri, hata ayıklama sırasında sağladıkları anında geri bildirimdir.MultiSim veya ModelSim gibi araçlar, sistem davranışının görsel temsillerini sunar ve girişlerdeki değişikliklerin zaman içinde çıktıları nasıl etkilediğini gösterir.Bu geri bildirim, sorunları daha hızlı belirlemenizi, hataları temel nedenlerine kadar takip etmenizi ve tasarımlarını buna göre ayarlamanızı sağlar.Örneğin, bir sistem zamanlama kısıtlamalarını karşılayamazsa veya belirli giriş dizileri altında beklenmedik davranışlar sergilerse, bir test bankası bu kusurları sistem fiziksel olarak oluşturulmadan hemen önce vurgulayabilir.Tasarım döngüsünün başlarında sorunları belirleyerek, test tezgahları pahalı yeniden işleme ve fiziksel prototipleme ihtiyacını azaltarak doğrulama sürecini kolaylaştırır.Bu erken aşama validasyonu, dijital sistemlerin hem işlevsel olarak doğru hem de koşullara dayanıklı olmasını sağlamaya yardımcı olur, bu da onları daha güvenilir hale getirir ve konuşlandırıldıktan sonra başarısızlık riskini azaltır.Bu şekilde, test bankaları teorik tasarımları sağlam hale getirmek için pratik bir araç görevi görür.

Gelişmiş Testbench Mimarisi

Gelişmiş test bankaları, karmaşık sistemleri yönetmek için ek bileşenler ekleyerek basit giriş-çıktı testinin ötesine geçer.Standart Testbench, üç anahtar parça içerir: A Uyarıcı giriş sinyalleri oluşturmak için Test Altında Tasarım (DUT), ki test edilen gerçek donanım ve bir Çıktı Monitörü Bu, çıktıları beklenen sonuçlara karşı kontrol eder.Bu bileşenler, dijital tasarımların daha kapsamlı ve doğru doğrulanmasını sağlamak için birlikte çalışır.

Testbench doğruluğunun iyileştirilmesi, bir tasarımın farklı senaryolarda güvenilir bir şekilde performans göstermesini sağlayan tekniklerin kullanılmasını içerir. Randomize test Sistemin çeşitli koşullar altında stabilitesini doğrulamak için öngörülemeyen giriş modelleri sunar. Edge Case Testi Sistemin hatalarla karşılaşma olasılığının yüksek olduğu sınır durumlarına odaklanır.Son olarak, Regresyon testi Değişikliklerden sonra testlerin yeniden çalıştırılmasını içerir, yeni sorunun getirilmediğini doğrulamak için sistemin zaman içinde tutarlı ve hatasız kalmasını sağlar.

Komut Dosyası Test Tebekleri

Verilog veya VHDL'de verimli ve güvenilir test tezgahları oluşturmak için en iyi uygulamaları izleyin.Önce temel işlevselliği test ederek ve yavaş yavaş daha karmaşık senaryolar ekleyerek basitçe başlatın, ardından genişletin.Her bölümü açıkça açıklayarak komut dosyalarınızın anlaşılmasını ve sürdürülmesini kolaylaştırmak için yorumları ve belgeleri kullanın.Son olarak, tekrarlayan görevleri ve giriş modellerini işlemek için döngü ve fonksiyonları kullanarak zamandan tasarruf etmek ve hataları azaltmak için mümkün olan yerlerde otomatikleştirin.

Hakkımızda

ALLELCO LIMITED

Daha fazla oku

Hızlı soruşturma

Lütfen bir soruşturma gönderin, hemen yanıt vereceğiz.

Dijital faz kilitli döngü (DPLL): Tasarım, Bileşenler ve İşlemler

2025/01/7'te

Modern bilgi işlemdeki RISC mimarisinin evrimi ve etkisi

2025/01/7'te

Popüler Mesajlar

-

Karmaşık talimat kümesi bilgisayarlar: Bilgi işlemini nasıl değiştirdi?

8000/04/18'te 147764

-

USB-C Pinout ve Özellikleri

2000/04/18'te 111989

-

Xilinx Birleşik Simülasyon İlkellerini Kullanma: FPGA Tasarımı ve Simülasyon için Kapsamlı Bir Kılavuz

1600/04/18'te 111351

-

Elektronikte Güç Kaynağı Gerilimleri: VCC, VDD, VEE, VSS ve GND'nin Anlamı

0400/04/18'te 83751

-

RJ45 Bağlayıcı Kılavuzu: Pinout, Kablo, Kablo Türleri ve Kullanımları

1970/01/1'te 79546

-

Modern elektrik sistemlerinde tel renk kodları için nihai kılavuz

Elektrik sistemlerimizin renkleri kullanma şekli sadece görünüm için değil.Her tel rengi artık belirli bir işlevi gösterir, bu da kurulum ve bakım sırasında elektrik bileşenlerini doğru bir şekilde...1970/01/1'te 66949

-

Puraj Valf Kılavuzu: İşlev, Belirtiler, Testler ve Optimal Motor Performansı için Değiştirme

Puraj valfi, bir otomobil sisteminin, atmosfere kaçmadan önce yakıt buharlarını yöneterek havayı temiz tutmaya yardımcı olan önemli bir parçasıdır.Bu sadece kirliliği azaltarak çevreye yardımcı olm...1970/01/1'te 63093

-

Kalite (Q) Faktörü: Denklemler ve Uygulamalar

İndüktörlerin ve rezonatörlerin radyo frekanslarını (RF) kullanan elektronik sistemlerde ne kadar iyi çalıştığını kontrol ederken kalite faktörü veya 'Q' önemlidir.'Q', bir devrenin enerji kaybını ...1970/01/1'te 63028

-

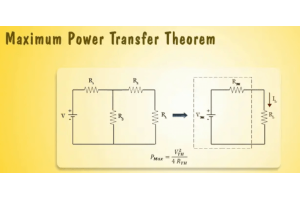

Maksimum güç transfer teoremiyle en yüksek performansı elde etmek

Maksimum güç aktarımı teoremi, bir kaynaktan akü veya jeneratör gibi enerjinin bağlı bir yüke nasıl aktığını açıklar.Yükün en fazla gücü aldığı tam durumu gösterir.Bu makale, teoremin ne anlama gel...1970/01/1'te 54092

-

A23 Pil Özellikleri ve Uyumluluk

A23 pil, yüksek voltajlı küçük, silindir şeklindeki bir pildir.23A, 23ae veya Mn21 olarak da adlandırılır, 12 volt ve AA veya AAA pillerinden çok daha yüksek çalışır.Özel tasarımı, küçük a...1970/01/1'te 52172