# 2.4 GHz RF SoC FOR WIRELESS DIGITAL AUDIO STREAMING CC8520, CC8521, CC8530 & CC8531 - PurePath™ Wireless

## **APPLICATIONS**

- Wireless high-quality digital audio

- Wireless point-to-point audio link

- Wireless (USB) headphones / headsets

- Wireless (USB) loudspeakers

- Wireless (USB) microphones

- Wireless 2.1 speaker systems

- CC852x supports up to 2 channels

- CC853x supports up to 4 channels

- CC85x1 supports USB

## FEATURES

**Built-in audio protocol**

- CD-quality uncompressed audio

- Excellent robustness and co-existence through multiple techniques

- Adaptive Frequency Hopping

- Forward Error Correction

- Buffering and Retransmission

- Error Concealment

- Optional high quality audio compression

- No software development needed when used in autonomous mode

## External system

- Can be used autonomously, or can be controlled by an external host MCU for greatest flexibility

- Seamless connection and control of external audio codecs, DACs/ADCs and digital audio amplifiers using I2S and I2C

- HID functions like power control, pairing, volume control, audio channel selection etc. can be mapped to I/Os

- RoHS compliant 6mm x 6mm QFN-40 package

## **RF** section

- 5 or 2 Mbps over-the-air data rate

- Bandwidth-efficient modulation format

- Excellent link budget with programmable output power up to +3.5 dBm and -83/-86 dBm sensitivity

- Seamless support for CC2590 range extender (+11dBm output power, -87dBm sensitivity)

- Suited for systems targeting compliance with worldwide radio frequency regulations: ETSI EN 300 328 and EN 300 440 class 2 (Europe), FCC CFR47 Part 15 (US) and ARIB STD-T66 (Japan)

**Digital audio support**

- Digital I2S audio interface supports 1 or 2 audio channels for the CC8520 and 1 to 4 audio channels for the CC8530 at sample rates of 32, 40.275, 44.1 and 48 kHz, and supports 16 and 24 bit word-widths

- USB audio support for 32, 44.1 and 48 kHz, and supports 16 and 24 bit word-widths

- Audio latency down to 10.7 ms

- Data side-channel allows data to be sent alongside the audio between external host processors

## USB

- Full-speed USB Audio device

- USB Basic Audio Device Class: HT1, HS1 and MT topologies (headphone, headset and microphone)

- USB Audio Device Class.

- Basic USB HID device class support for remote control, mouse and keyboard functionality

- Autonomous operation only.

## **Development tools**

- PC-based PurePath™ Wireless Configurator for CC85xx configuration

- CC85xx Family User Guide

- CC85XXDK audio development kit

- CC85XXDK-HEADSET development kit

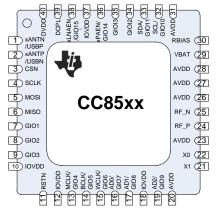

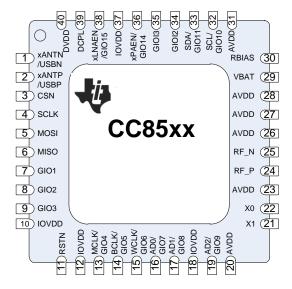

## QFN-40 PIN CONFIGURATION (TOP VIEW)

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PurePath<sup>™</sup> is a trademark for Texas Instruments

All other trademarks are the property of their respective owners.

#### DESCRIPTION

The PurePath<sup>™</sup> Wireless platform is a cost-effective and low-power solution optimized for wireless transmission of high-quality digital audio.

The CC85xx includes a robust built-in wireless audio transmission protocol and can control selected external audio devices. Utilizing numerous coexistence mechanisms allows the CC85xx to avoid interfering with, or being interfered by other 2.4 GHz radio systems.

The CC85xx operates autonomously, and can be used with or without an external MCU. An external host processor can be connected through SPI and control some aspects of its operation. The CC85xx interfaces easily with other TI audio ICs and DSPs (using I2S and DSP/TDM interfaces). More details can be found in the CC85xx Family User Guide [2].

| ADC   | Analog to Digital Converter                           | LED  | Light Emitting Diode                 |

|-------|-------------------------------------------------------|------|--------------------------------------|

| ARIB  | Association of Radio Industries and Businesses        | LNA  | Low Noise Amplifier                  |

| BER   | Bit Error Rate                                        | MISO | Master In Slave Out                  |

| CODEC | Coder/Decoder                                         | MOSI | Master Out Slave In                  |

| DAC   | Digital to Analog Converter                           | MCU  | Microcontroller                      |

| DSP   | Digital Signal Processor                              | PA   | Power Amplifier                      |

| EHIF  | External Host Interface                               | PCM  | Pulse Code Modulation                |

| ESD   | Electro Static Discharge                              | PER  | Packet Error Rate                    |

| ETSI  | European Telecommunications Standard Institute        | PLL  | Phase Lock Loop                      |

| FCC   | Federal Communications Commission                     | PM   | Protocol Master                      |

| FEC   | Forward Error Correction                              | PPW  | PurePath™ Wireless                   |

| FSK   | Frequency Shift Keying                                | PS   | Protocol Slave                       |

| FW    | Firmware                                              | RoHS | Restriction of Hazardous Substances  |

| HID   | Human Interface Device                                | RF   | Radio Frequency                      |

| I2C   | Inter-Integrated Circuit (serial communications bus)  | SLAC | Slightly Lossy Compression Algorithm |

| 12S   | Inter-IC Sound (serial bus for digital audio signals) | SPI  | Serial Peripheral Interface          |

| IEEE  | Institute of Electrical and Electronics Engineers     | SoC  | System-on-Chip                       |

| ISM   | Industrial, Scientific, Medical                       | STD  | Standard                             |

| JEDEC | Joint Electron Device Engineering Council             | TDM  | Time-Division Multiplexing           |

| LDO   | Low-Dropout Regulator                                 |      |                                      |

#### ABBREVIATIONS

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| PARAMETER                  | TEST CONDITIONS                                                             | Min  | Max                    | Unit |

|----------------------------|-----------------------------------------------------------------------------|------|------------------------|------|

| Supply voltage (2)         | All supply pins must have the same voltage                                  | -0.3 | 3.9                    | V    |

| Voltage on any digital pin |                                                                             | -0.3 | min(VDD +<br>0.3, 3.9) | V    |

| Input RF level             |                                                                             |      | 10                     | dBm  |

| Storage temperature range  |                                                                             | -40  | 125                    | °C   |

| ESD <sup>(3)</sup>         | All pads, according to human-body model<br>(HBM), JEDEC STD 22, method A114 |      | 2000                   | V    |

|                            | According to charged-device model (CDM),<br>JEDEC STD 22, method C101E      |      | 400                    | V    |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>(2)</sup> For CC8521 and CC8531 running on USB power, a LDO is needed to comply with these ratings.

<sup>(3)</sup> CAUTION: ESD sensitive device. Precaution should be used when handing the device in order to prevent permanent damage.

#### **RECOMMENDED OPERATING CONDITIONS, CC8520/CC8530**

| PARAMETER                                        | TEST CONDITIONS | Min | Max | Unit |

|--------------------------------------------------|-----------------|-----|-----|------|

| Operating ambient temperature range, $T_{\!\!A}$ |                 | -40 | +85 | °C   |

| Operating supply voltage                         |                 | 2.0 | 3.6 | V    |

#### **RECOMMENDED OPERATING CONDITIONS, CC8521/CC8531**

| PARAMETER                                  | TEST CONDITIONS | Min | Max | Unit |

|--------------------------------------------|-----------------|-----|-----|------|

| Operating ambient temperature range, $T_A$ |                 | -40 | +85 | °C   |

| Operating supply voltage (1)               |                 | 3.0 | 3.6 | V    |

<sup>(1)</sup> For CC8521 and CC8531 running on USB power, an LDO is needed to comply with these ratings.

#### **GENERAL CHARACTERISTICS**

Measured on Texas Instruments CC85xxEM reference designs with  $T_A = 25^{\circ}C$  and VDD = 3.3 V, unless otherwise noted.

| PARAMETER          | TEST CONDITION                                                                                                                                                                                 | MIN                | TYP                                       | MAX    | UNIT    |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------------------------------|--------|---------|

| RF frequency range |                                                                                                                                                                                                | 2400               |                                           | 2483.5 | MHz     |

| Data rate          | Shaped 8FSK<br>Shaped 2FSK                                                                                                                                                                     |                    | 5<br>2                                    |        | Mbps    |

| Audio latency      | Latency between I2S interface on audio source<br>and I2S interface on audio sink. Uncompressed<br>16 or 24 bit. Audio latency is programmable<br>using the PurePath Wireless Configurator [1]. | 512 <sup>(1)</sup> |                                           | 2048   | Samples |

| Audio sample rate  | Audio sample rate is programmable using the PurePath Wireless Configurator [1] <sup>(2)</sup>                                                                                                  |                    | 48<br>44.1<br>40.275 <sup>(3)</sup><br>32 |        | kHz     |

(1) Latencies below 768 samples only supported for some configurations

<sup>(2)</sup> ±2000ppm tolerance

<sup>(3)</sup> Not supported in USB mode. For USB Headset, dynamic sample rate change is not allowed.

#### ELECTRICAL CHARACTERISTICS, CC8520/CC8521/CC8530/CC8531

Measured on Texas Instruments CC85xxEM reference designs with  $T_A = 25^{\circ}C$  and VDD = 3.3 V, unless otherwise noted.

| PARAMETER                                            | TEST CONDITION                                                                                                                         | MIN | TYP | MAX | UNIT |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Current consumption, power down state                | Voltage regulator / crystal oscillator off – status<br>lost (POWERED_DOWN state)                                                       |     | 1   |     | μΑ   |

| Current consumption, headphone master <sup>(1)</sup> | Average current for a PurePath Wireless master<br>with I2S interface active, sourcing two PCM16<br>channels with maximum output power. |     | 29  |     | mA   |

| Current consumption, headphone slave <sup>(1)</sup>  | Average current for a PurePath Wireless slave<br>with I2S interface active, sinking two PCM16<br>channels with maximum output power    |     | 25  |     | mA   |

(1) Measured on Texas Instruments CC85xx EM reference designs and CC85XXDK. Sample rate 48 kHz, MCLK disabled. 5 Mbit mode

#### RF CHARACTERISTICS, CC8520/CC8521/CC8530/CC8531

Measured on Texas Instruments CC85xx EM reference designs with  $T_A = 25^{\circ}C$  and VDD = 3.3 V, unless otherwise noted.

| PARAMETER                                 | TEST CONDITION                                                                                                                                        | MIN | ТҮР        | MAX | UNIT |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------|-----|------|

| Output power                              | Maximum output power setting                                                                                                                          |     | 3.5        |     | dBm  |

| Receiver sensitivity <sup>(1)</sup>       | 5 Mbps<br>2 Mbps <sup>(2)</sup>                                                                                                                       |     | -83<br>-86 |     | dBm  |

| Saturation (maximum input level) $^{(1)}$ | 5 Mbps<br>2 Mbps <sup>(2)</sup>                                                                                                                       |     | -2<br>6    |     | dBm  |

|                                           | Adjacent channel, ±4MHz, wanted 3dB above<br>sensitivity. 5 Mbps<br>Adjacent channel, ±4MHz, wanted 3dB above<br>sensitivity. 2 Mbps <sup>(2)</sup>   |     | 8<br>20    |     | dB   |

| Selectivity                               | Alternate channel, ±8MHz, wanted 3dB above<br>sensitivity. 5 Mbps<br>Alternate channel, ±8MHz, wanted 3dB above<br>sensitivity. 2 Mbps <sup>(2)</sup> |     | 35<br>43   |     | dB   |

| Occupied bandwidth                        | 99% energy bandwidth. 5 Mbps<br>99% energy bandwidth. 2 Mbps <sup>(2)</sup>                                                                           |     | 3.8<br>3.2 |     | MHz  |

| Optimum load impedance                    | Differential impedance seen from the RF port (RF_P and RF_N) towards the antenna                                                                      |     | 70 + j30   |     | Ω    |

| Spurious emission                         | Suitable for systems targeting compliance with EN 300 328, EN 300 440 <sup>(3)</sup> , FCC CFR47 Part 15 and ARIB STD-T-66                            |     |            |     |      |

<sup>(1)</sup> Measured using data packets with 40 byte payload, 0.1% BER for 5 Mbit and 125 byte payload, 0.001% BED for 2 Mbit

<sup>(2)</sup> Typical data measured across 6 devices at room temperature.

<sup>(3)</sup> Systems with external antenna connector: Margins for passing conducted requirements at sub 1GHz frequencies can be improved by using a simple band-pass filter connected between matching network and RF connector (1.6 pF in parallel with 1.6 nH); this filter must be connected to a good RF ground.

#### ELECTRICAL CHARACTERISTICS, CC8520/CC8521/CC8530/CC8531+CC2590

Measured on Texas Instruments CC85xx+CC2590 EM reference designs with  $T_A = 25^{\circ}C$  and VDD = 3.3 V, unless otherwise noted.

| PARAMETER                                            | TEST CONDITION                                                                                               | MIN | ТҮР | MAX | UNIT |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Current consumption, power down state <sup>(1)</sup> | Voltage regulator / crystal oscillator off – status lost (POWERED_DOWN state)                                |     | 1   |     | μΑ   |

| Current consumption, headphone master <sup>(2)</sup> | Average current for a PurePath Wireless<br>master with I2S interface active, sourcing two<br>PCM16 channels. |     | 38  |     | mA   |

| Current consumption, headphone slave <sup>(2)</sup>  | Average current for a PurePath Wireless slave<br>with I2S interface active, sinking two PCM16<br>channels    |     | 28  |     | mA   |

<sup>(1)</sup> CC2590 power down current is 100 nA[4]

<sup>(2)</sup> Measured on Texas Instruments CC85xx+CC2590 EM reference designs and CC85XXDK. Sample rate 48 kHz, MCLK disabled. 5 Mbit mode

#### RF CHARACTERISTICS, CC8520/CC8521/CC8530/CC8531+CC2590

Measured on Texas Instruments CC85xx+CC2590 EM reference designs with T<sub>A</sub> = 25°C and VDD = 3.3 V, unless otherwise noted.

| PARAMETER                                       | TEST CONDITION                                                                                                             | MIN | TYP        | MAX | UNIT |

|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----|------------|-----|------|

| Output power                                    | Maximum output power setting                                                                                               |     | 11         |     | dBm  |

| Receiver sensitivity <sup>(1)</sup>             | 5 Mbps<br>2 Mbps <sup>(2)</sup>                                                                                            |     | -87<br>-90 |     | dBm  |

| Saturation (maximum input level) <sup>(1)</sup> | 5 Mbps                                                                                                                     |     | -12        |     | dBm  |

| Salaatiivittu                                   | Adjacent channel, ±4MHz, wanted 3dB above sensitivity. 5 Mbps                                                              |     | 9          |     | dB   |

| Selectivity                                     | Alternate channel, ±8MHz, wanted 3dB above sensitivity. 5 Mbps                                                             |     | 34         |     | uВ   |

| Spurious emission                               | Suitable for systems targeting compliance with EN 300 328, EN 300 440 <sup>(3)</sup> , FCC CFR47 Part 15 and ARIB STD-T-66 |     |            |     |      |

(1) Measured using data packets with 40 byte payload, 0.1% BER for 5 Mbit and 125 byte payload, 0.001% BER for 2 Mbit

<sup>(2)</sup> Typical data measured across 6 devices at room temperature.

<sup>(3)</sup> Systems with external antenna connector: Margins for passing conducted requirements at sub 1GHz frequencies can be improved by using a simple band-pass filter connected between matching network and RF connector (1.6 pF in parallel with 1.6 nH); this filter must be connected to a good RF ground.

#### 48-MHz CRYSTAL REQUIREMENTS

General parameters with  $T_A = 25^{\circ}C$  and VDD = 3.3 V, unless otherwise noted.

| PARAMETER                                             | TEST CONDITION | MIN | TYP | MAX | UNIT |

|-------------------------------------------------------|----------------|-----|-----|-----|------|

| Crystal frequency                                     |                |     | 48  |     | MHz  |

| Crystal frequency accuracy requirement <sup>(1)</sup> |                | -50 |     | 50  | ppm  |

| ESR Equivalent series resistance                      |                | -   |     | 60  | ohm  |

| C <sub>0</sub> Crystal shunt capacitance              |                | -   |     | 3   | pF   |

| C <sub>L</sub> Crystal load capacitance               |                | 15  | 16  | 17  | pF   |

<sup>(1)</sup> Including aging and temperature dependency

#### AUDIO CLOCK CHARACTERISTICS

$T_A = 25^{\circ}C$  and VDD = 3.3 V, unless otherwise noted.

| PARAMETER                  | TEST CONDITION                                               | MIN                  | TYP | MAX                   | UNIT |

|----------------------------|--------------------------------------------------------------|----------------------|-----|-----------------------|------|

| MCLK Frequency range       | Programmable using the PurePath Wireless<br>Configurator [1] | 32.F <sub>WCLK</sub> |     | 512-F <sub>WCLK</sub> |      |

| BCLK Frequency range       | Programmable using the PurePath Wireless<br>Configurator [1] | 32-F <sub>WCLK</sub> |     | 256-F <sub>WCLK</sub> |      |

| WCLK Frequency range       |                                                              | 31.936               |     | 48.096                | kHz  |

| RMS jitter (Output clocks) | RMS period jitter for 1000 periods                           |                      | 80  | 200                   | ps   |

SWRS091F - JUNE 2012

# SPI INTERFACE CHARACTERISTICS

$T_A = 25^{\circ}C$  and VDD = 3.3 V, unless otherwise noted.

| PARAMETER                               | TEST CONDITION                                                                                                                                                                         | MIN | TYP | MAX | UNIT |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| SCLK frequency                          |                                                                                                                                                                                        | 0   |     | 20  | MHz  |

| SCLK IOW                                |                                                                                                                                                                                        | 25  |     |     | ns   |

| SCLK high                               |                                                                                                                                                                                        | 25  |     |     | ns   |

| CSN high                                | Minimum time CSN must be high, if brought<br>high, between commands (it is not necessary to<br>bring CSN high between commands).                                                       | 50  |     |     | ns   |

| CSN falling edge to<br>SCLK rising edge | Distance from CSN asserted until first rising edge on SCLK.                                                                                                                            | 25  |     |     | ns   |

| SCLK falling edge to<br>CSN rising edge | Distance from last negative edge of SCLK in last word until CSN can be de-asserted.                                                                                                    | 100 |     |     | ns   |

| Inter-word spacing                      | Minimum distance in time from rising edge of SCLK for last bit in word <i>n</i> and the rising edge of SCLK for the first bit in word <i>n</i> +1.<br>Properly handles abutting words. | 50  |     |     | ns   |

| Hysteresis on SCLK                      | Hysteresis around trigger point of input buffer using a Schmitt trigger                                                                                                                |     | 100 |     | mV   |

| Slew rate on SCLK                       | Slew rate from 0.1-IOVDD to 0.9-IOVDD                                                                                                                                                  | 10  |     |     | V/µs |

## **VBAT CHARACTERISTICS**

$T_A = 25^{\circ}C$  and VDD = 3.3 V, unless otherwise noted.

| PARAMETER     | TEST CONDITIONS | Min | Max | Unit |

|---------------|-----------------|-----|-----|------|

| Input voltage |                 | 0   | 4.5 | V    |

## FLASH CHARACTERISTICS

$T_A = 25^{\circ}C$  and VDD = 3.3 V, unless otherwise noted.

| PARAMETER               | TEST CONDITIONS | Min | TYP | Max  | Unit   |

|-------------------------|-----------------|-----|-----|------|--------|

| Program/erase endurance |                 |     |     | 1000 | Cycles |

SWRS091F - JUNE 2012

# **1 PIN DESCRIPTION**

Figure 1 - CC85xx QFN-40 PIN CONFIGURATION

| PIN | PIN NAME      | PIN TYPE                   | DESCRIPTION                                                                              |

|-----|---------------|----------------------------|------------------------------------------------------------------------------------------|

| -   | GND           | Ground                     | The exposed die attach pad must be connected to a solid ground plane underneath the chip |

| 1   | xANTN<br>USBN | Digital I/O <sup>1</sup>   | CC85x0 Slaves: External antenna switch control<br>CC85x1: USB D- data line               |

| 2   | xANTP<br>USBP | Digital I/O <sup>1</sup>   | CC85x0 Slaves: External antenna switch control<br>CC85x1: USB D+ data line               |

| 3   | CS_N          | Digital Input<br>(pull-up) | Serial SPI configuration interface, active low chip select                               |

| 4   | SCLK          | Digital I/O <sup>1</sup>   | Serial SPI configuration interface, clock input/output                                   |

| 5   | MOSI          | Digital I/O <sup>1</sup>   | Serial SPI configuration interface, master data output, slave data input                 |

| 6   | MISO          | Digital I/O <sup>1</sup>   | Serial SPI configuration interface, master data input, slave data output.                |

| 7   | GIO1          | Digital I/O <sup>1</sup>   | General-purpose digital I/O pin 1                                                        |

|     |               |                            | Configurable with PurePath <sup>™</sup> Wireless Configurator                            |

| 8   | GIO2          | Digital I/O <sup>1</sup>   | General-purpose digital I/O pin 2                                                        |

| 9   | GIO3          | Digital I/O <sup>2</sup>   | General-purpose digital I/O pin 3                                                        |

|     |               |                            | Configurable with PurePath <sup>™</sup> Wireless Configurator                            |

| 10  | IOVDD         | Power<br>(I/O pads)        | Digital power supply for the digital I/Os in the SPI interface and GIO1-GIO3.            |

| 11  | RSTN          | Digital Input<br>(pull-up) | Active-low device reset                                                                  |

| 12  | IOVDD         | Power<br>(I/O pins)        | Digital power supply for the RSTN and MCLK digital I/O pins.                             |

| 13  | MCLK          | Digital I/O <sup>1</sup>   | Master clock output for external audio devices                                           |

|     | GIO4          |                            | General-purpose digital I/O pin 4                                                        |

| PIN | PIN NAME        | PIN TYPE                 | DESCRIPTION                                                                                                                                                                                                                   |

|-----|-----------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14  | BCLK            | Digital I/O <sup>1</sup> | I2S/DSP audio interface bit clock (in/out)                                                                                                                                                                                    |

|     | GIO5            |                          | General-purpose digital I/O pin 5                                                                                                                                                                                             |

| 15  | WCLK            | Digital I/O <sup>1</sup> | I2S/DSP audio interface word clock (in/out)                                                                                                                                                                                   |

|     | GIO6            |                          | General-purpose digital I/O pin 6                                                                                                                                                                                             |

| 16  | AD0             | Digital I/O <sup>1</sup> | I2S/DSP audio interface data line 0 (in/out)                                                                                                                                                                                  |

|     | GIO7            |                          | General-purpose digital I/O pin 7                                                                                                                                                                                             |

| 17  | AD1             | Digital I/O <sup>1</sup> | I2S/DSP audio interface data line 1 (in/out)                                                                                                                                                                                  |

|     | GIO8            |                          | General-purpose digital I/O pin 8                                                                                                                                                                                             |

| 18  | IOVDD           | Power<br>(I/O pins)      | Digital power supply for the digital I/Os in audio interface (BCLK-AD2).                                                                                                                                                      |

| 19  | AD2             | Digital I/O <sup>2</sup> | I2S/DSP audio interface data line 2 (in/out)                                                                                                                                                                                  |

|     | GIO9            |                          | Configurable with PurePath™ Wireless Configurator                                                                                                                                                                             |

| 20  | AVDD            | Power (Analog)           | 2.0-3.6V analog power supply connection                                                                                                                                                                                       |

| 21  | X1              | Analog I/O               | Crystal oscillator pin input, or external clock input (48 MHz)                                                                                                                                                                |

| 22  | X0              | Analog I/O               | Crystal oscillator pin output (48 MHz)                                                                                                                                                                                        |

| 23  | AVDD            | Power (Analog)           | Analog power supply connection                                                                                                                                                                                                |

| 24  | RF_P            | RF I/O                   | Positive differential RF input signal to LNA in receive mode                                                                                                                                                                  |

|     |                 |                          | Positive differential RF output signal from PA in transmit mode                                                                                                                                                               |

| 25  | RF_N            | RF I/O                   | Negative differential RF input signal to LNA in receive mode                                                                                                                                                                  |

|     |                 |                          | Negative differential RF output signal from PA in transmit mode                                                                                                                                                               |

| 26  | AVDD            | Power (Analog)           | Analog power supply connection                                                                                                                                                                                                |

| 27  | AVDD            | Power (Analog)           | Analog power supply connection                                                                                                                                                                                                |

| 28  | AVDD            | Power (Analog)           | Analog power supply connection                                                                                                                                                                                                |

| 29  | VBAT            | Analog input             | Battery voltage supervisor (threshold level programmable by external resistor to positive battery terminal)                                                                                                                   |

| 30  | RBIAS           | Analog output            | External precision bias resistor for reference current. 56 k $\Omega,\pm$ 1%                                                                                                                                                  |

| 31  | AVDD            | Power (Analog)           | Analog power supply connection (Guard ring AVDD connection for digital noise isolation)                                                                                                                                       |

| 32  | SCL             | Digital I/O <sup>1</sup> | I2C master clock line. Must be connected to external pull-up                                                                                                                                                                  |

|     | GIO10           |                          | General-purpose digital I/O pin 10                                                                                                                                                                                            |

| 33  | SDA             | Digital I/O <sup>1</sup> | I2C master data line. Must be connected to external pull-up                                                                                                                                                                   |

|     | GIO11           |                          | General-purpose digital I/O pin 11                                                                                                                                                                                            |

| 34  | GIO12           | Digital I/O <sup>1</sup> | General-purpose digital I/O pin 12                                                                                                                                                                                            |

| 35  | GIO13           | Digital I/O <sup>1</sup> | General-purpose digital I/O pin 13                                                                                                                                                                                            |

| 36  | xPAEN<br>GIO14  | Digital I/O <sup>2</sup> | Control external PA<br>General-purpose digital I/O pin 14                                                                                                                                                                     |

| 37  | IOVDD           | Power (I/O pads)         | Digital power supply for SCL-GIO15 pins.                                                                                                                                                                                      |

| 38  | xLNAEN<br>GIO15 | Digital I/O <sup>2</sup> | Control external LNA<br>General-purpose digital I/O pin 15                                                                                                                                                                    |

| 39  | DCPL            | Power (Digital)          | 1.7V-1.85 V linear voltage regulator output to which a 1 uF decoupling capacitor should be attached. For test-purposes an external digital supply voltage (1.62-1.98 V) can be applied here, bypassing the voltage regulator. |

|     |                 |                          | NOTE: The voltage regulator is intended for use with the CC85xx chip only. It cannot be used to provide supply voltage to other devices.                                                                                      |

| 40  | DVDD            | Power (Digital)          | Digital power supply for the linear voltage regulator.                                                                                                                                                                        |

Digital I/O pad with 4 mA source/sink capability.

Digital I/O pad with 20 mA source/sink capability.

SWRS091F - JUNE 2012

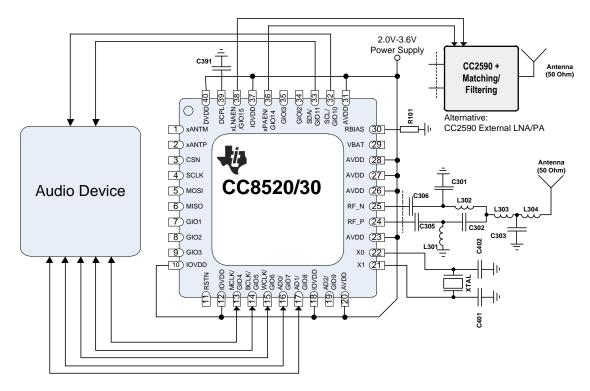

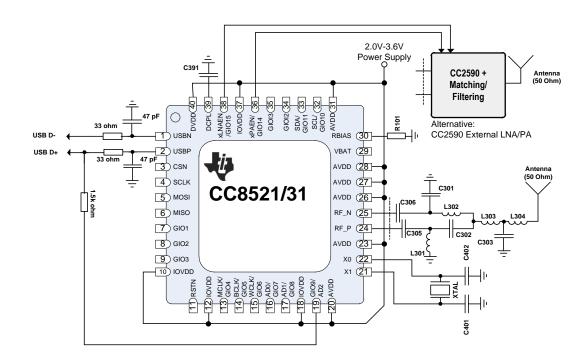

# 2 APPLICATION CIRCUIT

Figure 3 - CC8521/CC8531 Application Circuit

# **3 SYSTEM DESCRIPTION**

By employing proprietary technology, referred to as PurePath Wireless, the CC85xx device family provides robust, high-quality, short-range 2.4 GHz wireless digital audio streaming in low-cost single chip solutions.

Two or more devices form a PurePath Wireless audio network. Great care has been taken to ensure that this audio network provides gap-less and robust audio streaming in varied environments and that it can coexist amicably with existing wireless technologies in the crowded 2.4 GHz ISM band.

Most applications can be implemented without any software development and only require the CC85xx to be connected to an external audio source or sink (such as an audio codec, S/PDIF interface or class-D amplifier) and a few push buttons, switches or LED for human interaction. Advanced applications can interface a host processor or DSP directly to the CC85xx and directly stream audio and control most aspects of device and audio network operation. The complete list of supported audio devices can be found in the PurePath Wireless Configurator [1].

The PurePath Wireless Configurator [1], a PC-based configuration tool, is used to set up the desired functionality and parameters of the target system and then produces firmware images that subsequently must be programmed into the embedded flash memory of each CC85xx.

All devices in the CC85xx family interface seamlessly with the CC2590 RF range extender device to allow for even wider RF coverage and improved robustness in difficult environments.

| Revision | Date       | Description/Changes                                                                                                                                                                                                                                            |

|----------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SWRS091F | June 2012  | Added 2 Mbit mode (throughout document) and flash endurance<br>numbers. Lowered minimum latency. Added support for 24 bit data<br>width . Updated pin description.                                                                                             |

| SWRS091E | Dec 2011   | Added VBAT voltage info                                                                                                                                                                                                                                        |

| SWRS091D | July 2011  | Added info on CC8521 and CC8531                                                                                                                                                                                                                                |

| SWRS091C | March 2011 | Added info on CC8530. Updated current consumption numbers<br>and how they are measured. Storage temperature updated. Info on<br>supported codecs now in PurePath Wireless Configurator.                                                                        |

| SWRS091B | Sept 2010  | Add RF Characteristics for CC8520+CC2590EM. Moved the sections; Network topology, Coexistence, Audio Interface, Human Interaction drivers and external host interface to the <b>CC85xx</b><br><b>Family User's Guide [2].</b> Updated pin-out table and fig 1. |

| SWRS091A | March 2010 | First release                                                                                                                                                                                                                                                  |

# **4 DOCUMENT HISTORY**

# **5 REFERENCES**

- [1] <u>PurePath™ Wireless Configurator</u>

- [2] CC85xx Family User Guide

- [3] <u>CC-Debugger</u>

- [4] CC2590 Product folder

## PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|-------------------------------|---------------------|--------------|-------------------------|---------|

|                  |               |              |                    |      |                |                 | (6)                           |                     |              |                         |         |

| CC8520RHAR       | ACTIVE        | VQFN         | RHA                | 40   | 2500           | RoHS & Green    | NIPDAU                        | Level-3-260C-168 HR | -40 to 85    | CC8520                  | Samples |

| CC8520RHAT       | ACTIVE        | VQFN         | RHA                | 40   | 250            | RoHS & Green    | NIPDAU                        | Level-3-260C-168 HR | -40 to 85    | CC8520                  | Samples |

| CC8521RHAR       | ACTIVE        | VQFN         | RHA                | 40   | 2500           | RoHS & Green    | NIPDAU                        | Level-3-260C-168 HR | -40 to 85    | CC8521                  | Samples |

| CC8521RHAT       | ACTIVE        | VQFN         | RHA                | 40   | 250            | RoHS & Green    | NIPDAU                        | Level-3-260C-168 HR | -40 to 85    | CC8521                  | Samples |

| CC8530RHAR       | ACTIVE        | VQFN         | RHA                | 40   | 2500           | RoHS & Green    | NIPDAU                        | Level-3-260C-168 HR | -40 to 85    | CC8530                  | Samples |

| CC8530RHAT       | ACTIVE        | VQFN         | RHA                | 40   | 250            | RoHS & Green    | NIPDAU                        | Level-3-260C-168 HR | -40 to 85    | CC8530                  | Samples |

| CC8531RHAR       | ACTIVE        | VQFN         | RHA                | 40   | 2500           | RoHS & Green    | NIPDAU                        | Level-3-260C-168 HR | -40 to 85    | CC8531                  | Samples |

| CC8531RHAT       | ACTIVE        | VQFN         | RHA                | 40   | 250            | RoHS & Green    | NIPDAU                        | Level-3-260C-168 HR | -40 to 85    | CC8531                  | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW**: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

# PACKAGE OPTION ADDENDUM

(6) Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE MATERIALS INFORMATION

Texas Instruments

www.ti.com

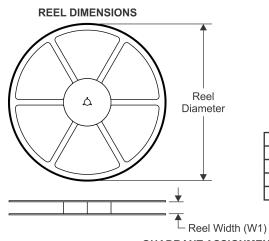

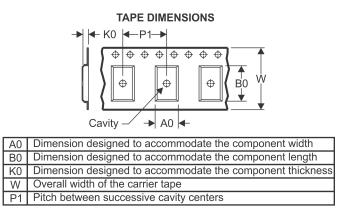

## TAPE AND REEL INFORMATION

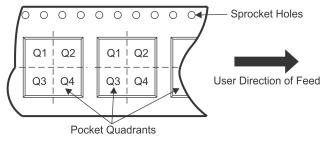

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| All dimensions are nominal<br>Device | 1    | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------------------------------|------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| CC8520RHAR                           | VQFN | RHA                | 40 | 2500 | 330.0                    | 16.4                     | 6.3        | 6.3        | 1.5        | 12.0       | 16.0      | Q2               |

| CC8521RHAR                           | VQFN | RHA                | 40 | 2500 | 330.0                    | 16.4                     | 6.3        | 6.3        | 1.5        | 12.0       | 16.0      | Q2               |

| CC8530RHAR                           | VQFN | RHA                | 40 | 2500 | 330.0                    | 16.4                     | 6.3        | 6.3        | 1.5        | 12.0       | 16.0      | Q2               |

| CC8531RHAR                           | VQFN | RHA                | 40 | 2500 | 330.0                    | 16.4                     | 6.3        | 6.3        | 1.5        | 12.0       | 16.0      | Q2               |

www.ti.com

# PACKAGE MATERIALS INFORMATION

25-Nov-2021

\*All dimensions are nominal

| Device     | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------|--------------|-----------------|------|------|-------------|------------|-------------|

| CC8520RHAR | VQFN         | RHA             | 40   | 2500 | 350.0       | 350.0      | 43.0        |

| CC8521RHAR | VQFN         | RHA             | 40   | 2500 | 350.0       | 350.0      | 43.0        |

| CC8530RHAR | VQFN         | RHA             | 40   | 2500 | 350.0       | 350.0      | 43.0        |

| CC8531RHAR | VQFN         | RHA             | 40   | 2500 | 350.0       | 350.0      | 43.0        |

# **RHA 40**

6 x 6, 0.5 mm pitch

# **GENERIC PACKAGE VIEW**

# VQFN - 1 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

# **RHA0040H**

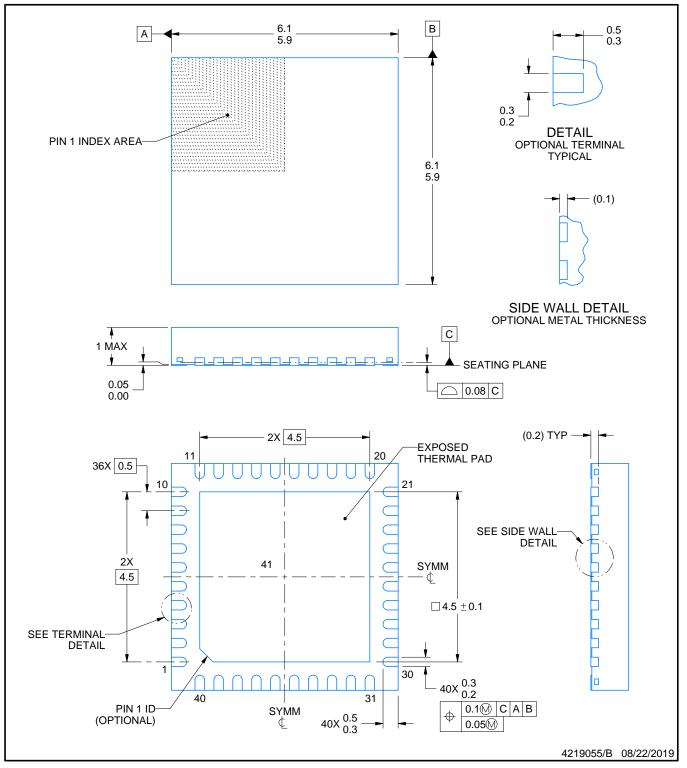

# **PACKAGE OUTLINE**

# VQFN - 1 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

# **RHA0040H**

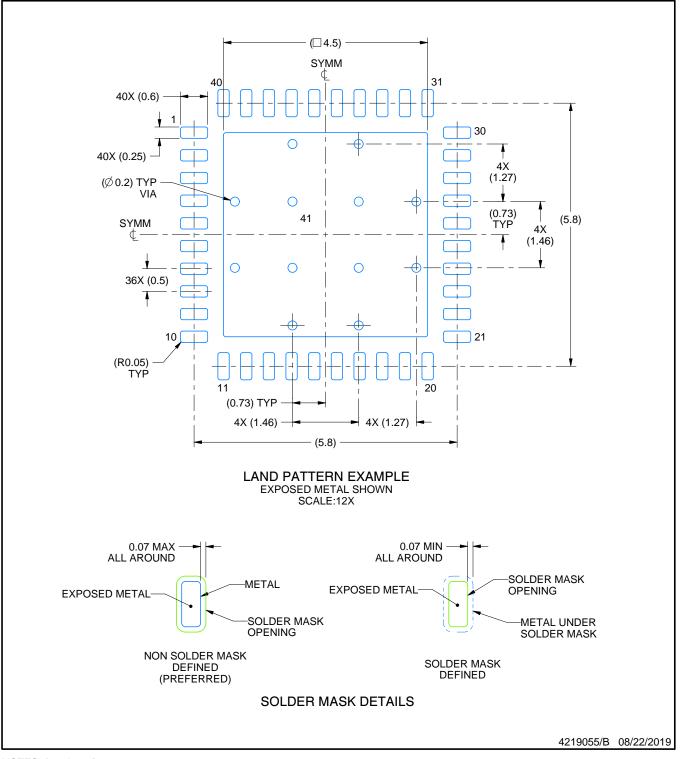

# **EXAMPLE BOARD LAYOUT**

# VQFN - 1 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

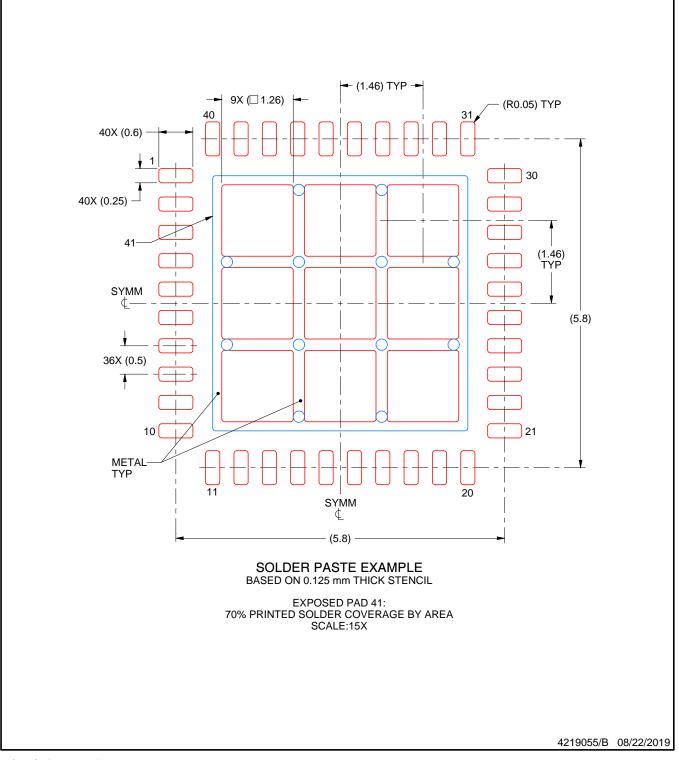

# **RHA0040H**

# **EXAMPLE STENCIL DESIGN**

# VQFN - 1 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2021, Texas Instruments Incorporated