Order

Now

**TPS66020, TPS66021**

SLVSEW8B-AUGUST 2019-REVISED DECEMBER 2019

Support &

Community

20

# TPS6602x Integrated Source and Sink Power Multiplexer with VBUS LDO Regulator

Technical

Documents

#### 1 Features

- Integrated 30 mΩ (typical), 32-V tolerant NFET 5-V source path, up to 3 A

- Integrated 22 mΩ (typical), 32-V tolerant NFET 4-V to 22-V sink path, up to 5 A

- Selectable current limit for 5-V source path

- · Built-in soft-start to limit in-rush currents

- Integrated high voltage VBUS LDO regulator (3.3-V or 5.0-V per device type)

- Optional VBUS overvoltage protection via pin configuration.

- System supply and VBUS undervoltage protection

- 5-V System supply overvoltage protection

- Overtemperature protection

- Reverse-current protection

- Fault pin with de-glitched fault reporting

- · Support for fast role swap

- IEC/UL Certificate No. US-34369-UL

Standards: IEC 62368-1 Ed. 2, UL 2367 Ed. 1

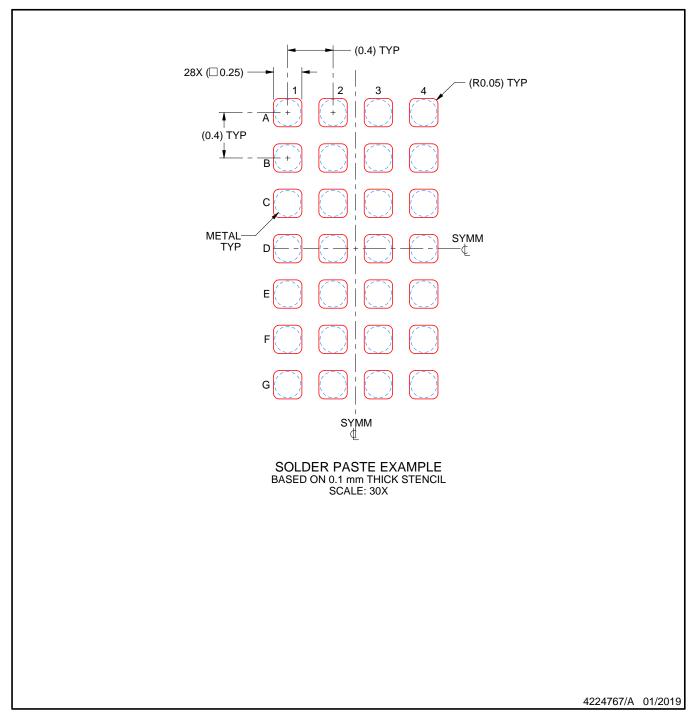

- Small footprint WCSP packaging, no HDI required.

## 2 Applications

- Desktop PC/motherboard

- Standard notebook PC

- Chromebook and WOA

- Docking station

- Port/cable adapters and dongles

## 3 Description

Tools &

Software

The TPS6602x is a full-featured power switch multiplexer that contains an integrated 5-V Source power path and a 4-V to 22-V Sink power path. The 5-V Source path limits the output current to a safe level by operating in a constant-current mode when the output load exceeds the selected current-limit path threshold. Each power supports overtemperature and reverse current protection. VBUS has overvoltage protection with its level being set by an optional external resistor divider. If no overvoltage protection is desired, it may be disabled by grounding the OVP terminal. The TPS6602x series supports a fault pin that indicates overcurrent and overtemperature events.

TPS6602x series also supports a high voltage VBUS LDO regulator (3.3-V or 5-V per device type) useful for supplying power to the device and other system components when operating in dead battery conditions. The TPS66020 regulates to 3.3-V and the TPS66021 regulates to 5-V.

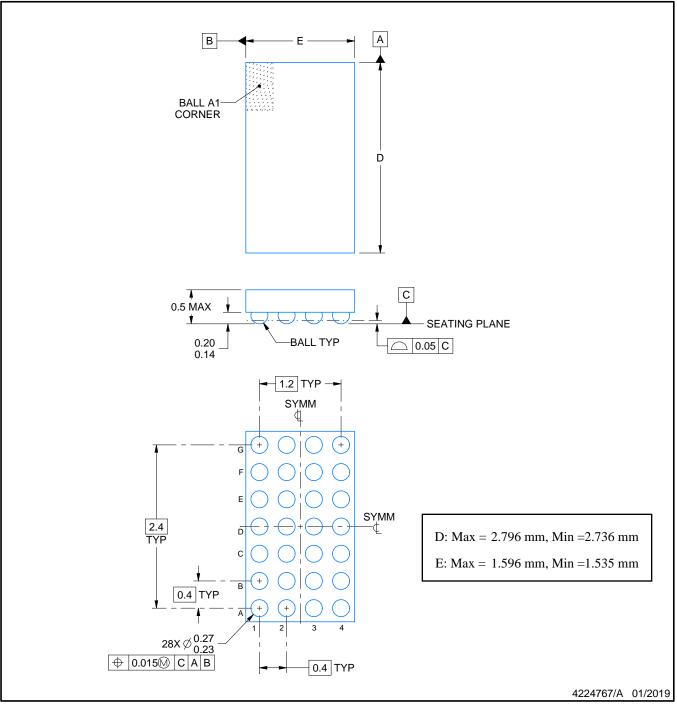

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)     |

|-------------|-----------|---------------------|

| TPS66020    |           | 1 606 mm v 2 806 mm |

| TPS66021    | WCSP (28) | 1.606 mm x 2.806 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

#### **Function Table**

| EN1 | EN0 | Device State                   |  |  |

|-----|-----|--------------------------------|--|--|

| 0   | 0   | Source and Sink paths disabled |  |  |

| 0   | 1   | Sink path enabled              |  |  |

| 1   | 0   | Source path enabled, 1.5 A     |  |  |

| 1   | 1   | Source path enabled, 3.0 A     |  |  |

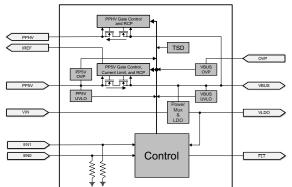

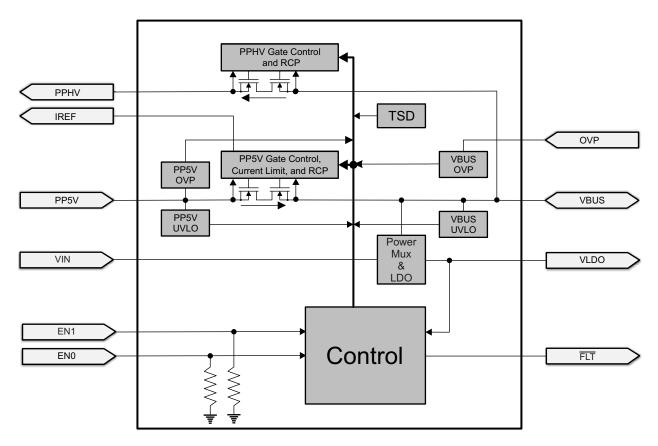

## TPS6602x Block Diagram

2

# Table of Contents

| 1 | Feat  | ures 1                                |

|---|-------|---------------------------------------|

| 2 | App   | lications 1                           |

| 3 | Desc  | cription 1                            |

| 4 | Revi  | sion History 2                        |

| 5 | Pin ( | Configuration and Functions 3         |

| 6 | Spec  | cifications 4                         |

|   | 6.1   | Absolute Maximum Ratings 4            |

|   | 6.2   | ESD Ratings 4                         |

|   | 6.3   | Recommended Operating Conditions      |

|   | 6.4   | Recommended Supply Load Capacitance 5 |

|   | 6.5   | Thermal Information 5                 |

|   | 6.6   | PP5V Power Switch Characteristics 6   |

|   | 6.7   | PPHV Power Switch Characteristics7    |

|   | 6.8   | Power Path Supervisory 7              |

|   | 6.9   | VBUS LDO Characteristics 8            |

|   | 6.10  | Thermal Shutdown Characteristics 8    |

|   | 6.11  | Input-output (I/O) Characteristics9   |

|   | 6.12  | Power Consumption Characteristics9    |

|   | 6.13  | Typical Characteristics 11            |

| 7 | Para  | meter Measurement Information 13      |

| 0  | Data | iled Departmention                              | 4.4 |

|----|------|-------------------------------------------------|-----|

| 8  |      | iled Description                                |     |

|    | 8.1  | Overview                                        |     |

|    | 8.2  | Functional Block Diagram                        |     |

|    | 8.3  | Feature Description                             | 14  |

|    | 8.4  | Device Functional Modes                         | 21  |

| 9  | Арр  | lication and Implementation                     | 31  |

|    | 9.1  | Application Information                         | 31  |

|    | 9.2  | Typical Application                             | 31  |

| 10 | Pow  | ver Supply Recommendations                      | 36  |

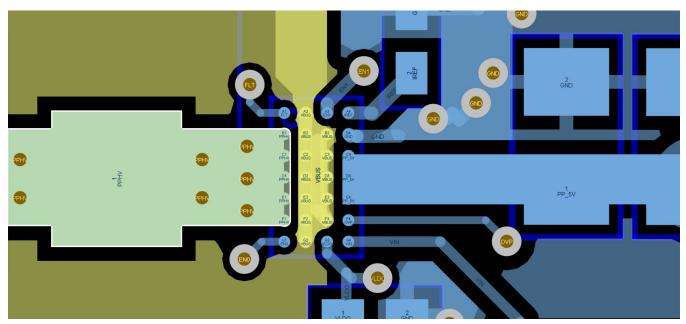

| 11 | Lay  | out                                             | 37  |

|    | 11.1 | Layout Guidelines                               | 37  |

|    | 11.2 | Layout Example                                  | 37  |

| 12 | Dev  | ice and Documentation Support                   | 38  |

|    | 12.1 | Related Links                                   | 38  |

|    | 12.2 | Receiving Notification of Documentation Updates | 38  |

|    | 12.3 | Support Resources                               | 38  |

|    | 12.4 | Trademarks                                      | 38  |

|    | 12.5 | Electrostatic Discharge Caution                 | 38  |

|    | 12.6 | Glossary                                        | 38  |

| 13 | Mec  | hanical, Packaging, and Orderable               |     |

|    | Info | rmation                                         | 38  |

|    |      |                                                 |     |

# 4 Revision History

| Changes from Revision A (September 2019) to Revision B | Page |

|--------------------------------------------------------|------|

| Changed from Advance Information to Production Data    |      |

| Changes from Original (August 2019) to Revision A      | Page |

| Updated Applications section with links                |      |

| Added Typical Characteristics section                  | 11   |

| Added Application Curves section                       |      |

www.ti.com

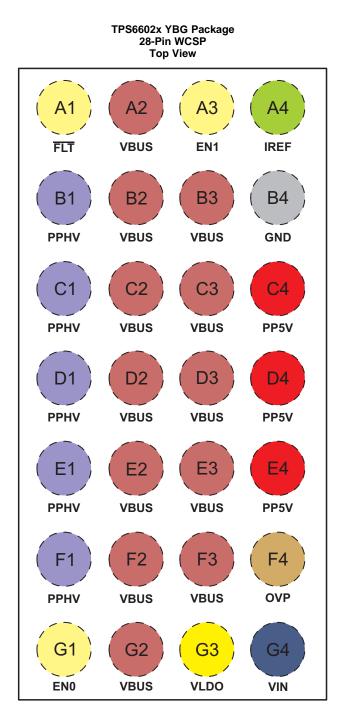

## 5 Pin Configuration and Functions

#### **Pin Functions**

| P    | in                    | I/O   | Depat State | Description                                                       |

|------|-----------------------|-------|-------------|-------------------------------------------------------------------|

| Name | No.                   | 1/0   | Reset State | Description                                                       |

| PP5V | C4, D4, E4            | Power | Off         | 5-V System Supply to VBUS. Bypass with capacitance CPP5V to GND.  |

| PPHV | B1, C1, D1,<br>E1, F1 | Power | Off         | HV System Supply from VBUS. Bypass with capacitance CPPHV to GND. |

Copyright © 2019, Texas Instruments Incorporated

Submit Documentation Feedback 3

TEXAS INSTRUMENTS

www.ti.com

### Pin Functions (continued)

| F    | Pin                                                     |                   | Decet State | Description                                                                                                                          |

|------|---------------------------------------------------------|-------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Name | No.                                                     | I/O               | Reset State | Description                                                                                                                          |

| VBUS | A2, B2, B3,<br>C2, C3, D2,<br>D3, E2, E3,<br>F2, F3, G2 | Power             | -           | 5-V to 20-V nominal input supply to PPHV or 5-V output supply from PP5V. Bypass with capacitance CVBUS to GND.                       |

| VIN  | G4                                                      | Power             | -           | Device input supply. Bypass with capacitance CVIN to GND.                                                                            |

| VLDO | G3                                                      | Power             | -           | VIN supply or VBUS LDO regulated supply output from power multipexer. Bypass with capacitance CVLDO to GND.                          |

| GND  | B4                                                      | Ground            | -           | Ground. Connect all pins to ground plane.                                                                                            |

| OVP  | F4                                                      | Analog            | -           | Selects VBUS OVP. Tie pin to VBUS resistor divider output to set desired VBUS OVP level. Tie pin to GND to remove VBUS OVP function. |

| EN1  | A3                                                      | Digital Input     | Pull-down   | Enable control signal for PPHV Sink and PP5V Source paths. Internal pull-down.                                                       |

| EN0  | G1                                                      | Digital Input     | Pull-down   | Enable control signal for PPHV Sink and PP5V Source paths. Internal pull-down.                                                       |

| IREF | A4                                                      | Analog            |             | Used to set the PP5V source path current limit bias using an external resistor tied to GND.                                          |

| FLT  | A1                                                      | Digital<br>Output | Hi-Z        | Fault Output Indicator. Active low. This pin is a true open-drain (no PMOS). Float pin when unused.                                  |

## 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                  | PARAMETER                                                      | MIN  | МАХ                | UNIT |

|----------------------------------|----------------------------------------------------------------|------|--------------------|------|

| Terminal voltage range (2)       | PP5V, EN0 <sup>(3)</sup> , EN1 <sup>(3)</sup> , FLT, VIN, VLDO | -0.3 | 6.2                | V    |

| Terminal voltage range (2)       | OVP                                                            | -0.3 | VBUS               | V    |

| Terminal voltage range (2)       | VBUS, power path disabled (stand off voltage)                  | -0.5 | 32                 | V    |

| Terminal voltage range (2)       | VBUS, power path enabled <sup>(4)</sup>                        | -0.5 | 26                 | V    |

| Terminal voltage range (2)       | PPHV                                                           | -0.3 | 26                 | V    |

| Terminal voltage range (2)       | IREF                                                           | -0.3 | 4.5                | V    |

| Terminal positive source current | IREF                                                           |      | Internally limited | mA   |

| Terminal positive source surrent | VLDO sourced from VBUS VLDO                                    |      | Internally limited | mA   |

| Terminal positive source current | VLDO sourced from VIN                                          |      | 50                 | mA   |

| Storage temperature              |                                                                | -55  | 150                | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to network GND. All GND pins must be connected directly to the GND plane of the board.

(3) EN0 and EN1 each have an internal voltage clamp and may be driven above the absolute maximum voltage rating up to EN\_CLAMP maximum specification if current is limited to less than 100µA.

(4) For VBUS, a TVS protection with a break down voltage falling between the Recommended and Absolute maximum ratings is recommended, such as the TVS2200.

## 6.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

| V                  | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±1000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | v    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                     |                                           |                                        | MIN   | MAX   | UNIT  |

|---------------------|-------------------------------------------|----------------------------------------|-------|-------|-------|

| V                   | Input voltage range <sup>(1)</sup>        | VIN, TPS66020 only.                    | 2.85  | 3.6   | V     |

| V <sub>VIN</sub>    | input voltage range V                     | VIN, TPS66021 only.                    | 4.5   | 5.5   | V     |

| V <sub>PP5V</sub>   | Input voltage range (1)                   | PP5V                                   | 4.9   | 5.5   | V     |

| V <sub>PPHV</sub>   | Output voltage range (1)                  | PPHV                                   | 0     | 22    | V     |

| V <sub>VBUS</sub>   | Output voltage range (1)                  | VBUS when sourcing                     | 0     | 5.5   | V     |

| V <sub>VBUS</sub>   | Input voltage range (1)                   | VBUS when sinking                      | 4     | 22    | V     |

| V <sub>EN</sub>     | Input voltage range (1)                   | EN0, EN1                               | 0     | 5.5   | V     |

| VFLT                | Output voltage range (1)                  | FLT                                    | 0     | 5.5   | V     |

| I <sub>O_PP5V</sub> | Continuous current from PP5V to VBUS      | $T_J = 105^{\circ}C$                   |       | 3     | А     |

|                     | Continuous current from VBUS to           | $T_J = 105^{\circ}C$                   |       | 4     | А     |

| IO_PPHV             | PPHV                                      | $T_J = 100^{\circ}C$                   |       | 5     | А     |

| I <sub>O_VLDO</sub> | Output current from VBUS LDO              |                                        |       | 30    | mA    |

| R <sub>IREF</sub>   | External resistor current limit reference | $75k\Omega \pm 1\%$ overall tolerance  | 74.25 | 75.75 | kΩ    |

| TJ                  | Operating junction temperature            |                                        | -10   | 125   | °C    |

| RR_PP5V             | Maximum ramp rate on PP5V input           | supply                                 | -2    | 2     | V/µs  |

| RR_PPHV             | Maximum ramp rate on PPHV input           | Maximum ramp rate on PPHV input supply |       | 2     | V/µs  |

| RR_VBUS             | Maximum ramp rate on VBUS input           | Maximum ramp rate on VBUS input supply |       | 2     | V/µs  |

| RR_VIN              | Maximum ramp rate on VIN input su         | pply                                   |       | 30    | mV/µs |

(1) All voltage values are with respect to network GND. GND pin must be connected directly to the ground plane of the board.

#### 6.4 Recommended Supply Load Capacitance

over operating free-air temperature range (unless otherwise noted)

|       | MIN                                        | TYP | MAX | UNIT |    |

|-------|--------------------------------------------|-----|-----|------|----|

| CVIN  | Capacitance on VIN                         | 1   |     |      | μF |

| CVLDO | Capacitance on VLDO                        | 2.5 | 4.7 | 10   | μF |

| CVBUS | Capacitance on VBUS                        | 1   |     | 10   | μF |

| CPP5V | Capacitance on PP5V                        | 2.5 | 4.7 |      | μF |

| CPPHV | Capacitance present on PPHV <sup>(2)</sup> | 1   | 47  | 100  | μF |

(1) Capacitance values do not include any derating factors. For example, if 5.0 µF is required and the external capacitor value reduces by 50% at the required operating voltage, then the required external capacitor value would be 10 µF.

(2) This capacitance represents the system side load capacitance that may be seen by the device e.g. from a typical battery charging system. Discrete capacitance is not required for proper operation.

#### 6.5 Thermal Information

|                      |                                                                       | TPS6602x   |      |

|----------------------|-----------------------------------------------------------------------|------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                                         | YBG (WCSP) | UNIT |

|                      |                                                                       | 28 PINS    |      |

| $R_{\theta JA, EFF}$ | Effective Junction-to-ambient thermal resistance <sup>(2)</sup>       | 44.3       | °C/W |

| $R_{\thetaJA}$       | Junction-to-ambient thermal resistance                                | 62.7       | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance                             | 0.4        | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance                                  | 13.8       | °C/W |

| ΨJT                  | Junction-to-top characterization parameter                            | 0.2        | °C/W |

| Ψјв                  | Junction-to-board characterization parameter                          | 13.7       | °C/W |

| ΨJB,EFF              | Effective Junction-to-board characterization parameter <sup>(2)</sup> | 14.5       | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

(2) Models based on typical application layout.

Copyright © 2019, Texas Instruments Incorporated

SLVSEW8B-AUGUST 2019-REVISED DECEMBER 2019

www.ti.com

### 6.6 **PP5V Power Switch Characteristics**

Operating under these conditions unless otherwise noted: -10 °C  $\leq$  T<sub>J</sub>  $\leq$  125 °C, 2.85V  $\leq$  V<sub>VIN</sub>  $\leq$  5.5V, R<sub>IREF</sub> = 75 k $\Omega$  ±1% overall tolerance, 4.9V  $\leq$  V<sub>P5V</sub>  $\leq$  5.5V

|                             | PARAMETER                                                                                                    | TEST CONDITIONS                                                                                                                                                                                    | MIN  | TYP  | MAX  | UNIT |

|-----------------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| P                           | Resistance from PP5V to VBUS                                                                                 | $I_{LOAD} = 1 A$ , PP5V = 5.0V, T <sub>J</sub> = 25°C, SRC 1P5A or SRC 3P0A state.                                                                                                                 |      | 30   | 35   | mΩ   |

| R <sub>PP5V</sub>           |                                                                                                              | $I_{LOAD}$ = 1 A, PP5V = 5.0V, -10 °C ≤ T <sub>J</sub> ≤ 125 °C, SRC 1P5A or SRC 3P0A state.                                                                                                       |      | 30   | 50   | mΩ   |

| I <sub>SC_IREF</sub>        | Short circuit current from VBUS with IREF terminal shorted.                                                  | V <sub>IREF</sub> = 0V, SRC 1P5A or SRC 3P0A state.                                                                                                                                                |      |      | 8    | А    |

| V                           | Output voltage                                                                                               | SRC 1.5A state                                                                                                                                                                                     |      | 0.56 |      | V    |

| V <sub>IREF</sub>           |                                                                                                              | SRC 3.0A state                                                                                                                                                                                     |      | 1.13 |      | V    |

| ILIM_PP5V_1P5               | Current limit for 1.5A setting                                                                               | SRC 1.5A state                                                                                                                                                                                     | 1.60 | 1.74 | 1.87 | А    |

| ILIM_PP5V_3P0               | Current limit for 3.0A setting                                                                               | SRC 3.0A state                                                                                                                                                                                     | 3.2  | 3.45 | 3.7  | А    |

| ILIMPP5VF                   | Difference between current limit<br>and current limit fault flag assertion,<br>$I_{LIM5VF} \leq I_{LIM5V}$ . | SRC 1P5A or SRC 3P0A state.<br>PP5V = 5V. Sweep load current<br>and monitor FLT transition from 1<br>to 0 (50% point). $C_{FLT}$ = 20pF, $R_{PU}$<br>= 10 k $\Omega$ to VLDO.                      |      | 12   |      | mA   |

| t <sub>ILIMIT_FLT</sub>     | Time from PP5V current limit detected until FLT asserted low.                                                | SRC 1P5A or SRC 3P0A state.<br>PP5V = 5V. Sweep load current<br>and monitor FLT transition from 1<br>to 0 (50% point). $C_{FLT}$ = 20pF, $R_{PU}$<br>= 10 k $\Omega$ to VLDO.                      | 4    | 10   | 16   | ms   |

| V <sub>PP5V_RCP</sub>       | Maximum voltage due to reverse current. Source path disables due to RCP comparator.                          | SRC 1P5A or SRC 3P0A state.<br>$V_{PP5V} = 5.5V$ , ramp $V_{VBUS}$ from<br>5.5V to 21V at 75 V/ms, $C_{PP5V} =$<br>$47\mu$ F, measure $V_{PP5V}$                                                   |      |      | 5.8  | V    |

| V <sub>PP5V_RCP_OVP</sub>   | Maximum voltage due to reverse current. Source path disables due to OVP protection on PP5V.                  | SRC 1P5A or SRC 3P0A state.<br>$V_{PP5V} = 5.5V$ , ramp $V_{VBUS}$ from<br>5.5V to 21V at 5 V/ms, $C_{PP5V} =$<br>4.7µF, measure $V_{PP5V}$                                                        |      |      | 6.25 | v    |

| V <sub>RCP_THRES_PP5V</sub> | Reverse current blocking voltage threshold for PP5V switch                                                   |                                                                                                                                                                                                    | 25   | 35   | 45   | mV   |

| t <sub>OS_PP5V</sub>        | Response time to VBUS short<br>circuit                                                                       | VBUS to GND through $10m\Omega$                                                                                                                                                                    |      | 2.0  |      | μs   |

| t <sub>ON_PP5V</sub>        | PP5V enable time.                                                                                            | $\begin{array}{l} R_L = 100\Omega, \ V_{PP5V} = 5V, \ C_L = 0, \\ Transition \ from \ DISABLED \ state \ to \\ SRC \ 1.5A \ state, \ V_{VBUS} \ reaches \\ 90\% \ of \ final \ value. \end{array}$ | 2.6  | 4.5  | 5.3  | ms   |

| toff_pp5v                   | PP5V disable time.                                                                                           | $\begin{array}{l} R_L = 100\Omega,  V_{PP5V} = 5V,  C_L = 0, \\ Transition  from  SRC  1.5A   or  SRC \\ 3.0A  state  to  DISABLED  state, \\ V_{VBUS}  at  10\%  of  final  value. \end{array}$   | 0.5  | 0.7  | 1.2  | ms   |

| t <sub>RISE_PP5V</sub>      | VBUS from 10% to 90% of final value                                                                          | $R_L = 100\Omega$ , $V_{PP5V} = 5V$ , $C_L=0$ ,<br>Transition from DISABLED state to<br>SRC 1.5A state                                                                                             | 0.5  | 0.9  | 1.5  | ms   |

| t <sub>FALL_</sub> PP5V     | VBUS from 90% to 10% of initial value                                                                        | $\begin{array}{l} R_L = 100\Omega, \ V_{PP5V} = 5V, \ C_L = 0, \\ Transition \ from \ SRC \ 1.5A \ or \ SRC \\ 3.0A \ state \ to \ DISABLED \ state \end{array}$                                   | 0.1  | 0.16 | 0.25 | ms   |

### 6.7 PPHV Power Switch Characteristics

Operating under these conditions unless otherwise noted: -10 °C  $\leq$  T<sub>J</sub>  $\leq$  125 °C, 2.85V  $\leq$  V<sub>VIN</sub>  $\leq$  5.5V, R<sub>IREF</sub> = 75 k $\Omega$  ±1% overall tolerance

|                             | PARAMETER                                                             | TEST CONDITIONS                                                                                                                                                                                            | MIN | TYP | MAX | UNIT |

|-----------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

|                             |                                                                       | $I_{LOAD} = 1 \text{ A}, T_{J} = 25 \text{ °C}, \text{ SNK state.}$                                                                                                                                        |     | 22  | 26  | mΩ   |

| R <sub>PPHV</sub>           | Resistance from PPHV to VBUS                                          | $I_{LOAD} = 1 \text{ A}, -10 \text{ °C} \le T_J \le 125 \text{ °C},$<br>SNK state.                                                                                                                         |     | 22  | 45  | mΩ   |

| V <sub>PPHV_RCP</sub>       | Maximum voltage due to reverse current during RCP response.           | SNK state, $V_{VBUS}$ = 5.5V, ramp $V_{PPHV}$ from 5.5V to 21V at 100 V/ms, $C_{VBUS}$ = 10µF, measure $V_{VBUS}$                                                                                          |     |     | 5.8 | V    |

| V <sub>PPHV_OVP</sub>       | Maximum voltage rise due to reverse current during VBUS OVP response. | SNK state, $V_{VBUS}$ = 5.5V, set $V_{OVP}$<br>= 6V, ramp $V_{VBUS}$ from 5.5V to 21V<br>at 100 V/ms, C <sub>PPHV</sub> = 4.7µF,<br>measure $V_{PPHV}$                                                     |     |     | 6.2 | V    |

| V <sub>RCP_THRES_PPHV</sub> | Reverse current blocking voltage threshold for PPHV switch            |                                                                                                                                                                                                            | 2   | 6   | 10  | mV   |

| SS                          | Soft-start slew rate                                                  | Transition from DISABLED state to SNK state, $V_{VBUS} = 5V$ , $C_{PPHV} = 100\mu$ F. Measure slew rate on PPHV.                                                                                           | 0.2 |     | 0.6 | V/ms |

| t <sub>on_pphv</sub>        | PPHV enable time including Soft-<br>start.                            | $\begin{array}{l} R_{PPHV} = 100\Omega,  V_{VBUS} = 5V,  C_{PPHV} \\ = 100  \muF.  \text{Transition from} \\ DISABLED  \text{state to SNK state,} \\ V_{PPHV}  \text{at 90\% of final value.} \end{array}$ | 9   | 15  | 29  | ms   |

| t <sub>off_pphv</sub>       | PPHV disable time.                                                    | $R_{PPHV} = 100\Omega$ , $V_{VBUS} = 5V$ , $C_{PPHV} = 4.7 \mu$ F. Transition from SNK state to DISABLED state, $V_{PPHV}$ falls to 4.5V.                                                                  | 0.9 | 2.2 | 4.3 | ms   |

## 6.8 Power Path Supervisory

Operating under these conditions unless otherwise noted: -10 °C  $\leq$  T<sub>J</sub>  $\leq$  125 °C, 2.85V  $\leq$  V<sub>VIN</sub>  $\leq$  5.5V, R<sub>IREF</sub> = 75 k $\Omega$  ±1% overall tolerance

|               | PARAMETER                                                                      | TEST CONDITIONS             | MIN  | TYP | MAX  | UNIT |

|---------------|--------------------------------------------------------------------------------|-----------------------------|------|-----|------|------|

| UV VIN R      | Undervoltage threshold for VIN. VBUS                                           | VIN rising, TPS66020 only.  | 2.45 |     | 2.75 | V    |

|               | LDO disables when threshold reached.                                           | VIN rising, TPS66021 only.  | 3.89 |     | 4.40 | V    |

|               | Undervoltage threshold for VIN. Device                                         | VIN falling, TPS66020 only. | 2.35 |     | 2.65 | V    |

| UV_VIN_F      | resets.                                                                        | VIN falling, TPS66021 only. | 3.79 |     | 4.30 | V    |

| UVH_VIN       | Undervoltage hysteresis for VIN.                                               |                             |      | 100 |      | mV   |

| UV_VBUS_R     | Undervoltage threshold for VBUS. PPHV switch disabled unitl threshold reached. | VBUS rising                 | 3.35 |     | 3.75 | V    |

| UV_VBUS_F     | Undervoltage threshold for VBUS. PPHV switch disables when threshold reached.  | VBUS falling                | 3.15 |     | 3.55 | V    |

| UVH_VBUS      | Undervoltage hysteresis for VBUS                                               |                             |      | 200 |      | mV   |

| OVP_REF       | OVP reference voltage.                                                         |                             | 0.93 | 1   | 1.07 | V    |

| UV_PP5V_R     | Undervoltage threshold for PP5V. PP5V switch disabled unitl threshold reached. | PP5V rising                 | 3.9  |     | 4.5  | V    |

| UVH_PP5V      | Undervoltage hysteresis for PP5V                                               |                             |      | 100 |      | mV   |

| UV_PP5V_F     | Undervoltage threshold for PP5V. PP5V swtch disables when threshold reached.   | PP5V falling                | 3.8  |     | 4.4  | V    |

| OV_PP5V_R     | Overvoltage threshold for PP5V. PP5V switch disabled if threshold reached.     | PP5V rising                 | 5.60 | 5.9 | 6.2  | V    |

| OV_PP5V_F     | Overvoltage threshold for PP5V. PP5V switch enabled if threshold reached.      | PP5V falling                | 5.50 | 5.8 | 6.1  | V    |

| OVH_PP5V      | Overvoltage hysteresis for PP5V                                                |                             |      | 100 |      | mV   |

| VFWD_DROP_VIN | Forward voltage drop across<br>VIN to VLDO switch                              | I <sub>VLDO</sub> = 35 mA   |      |     | 90   | mV   |

Copyright © 2019, Texas Instruments Incorporated

7

### **Power Path Supervisory (continued)**

Operating under these conditions unless otherwise noted: -10 °C  $\leq$  T<sub>J</sub>  $\leq$  125 °C, 2.85V  $\leq$  V<sub>VIN</sub>  $\leq$  5.5V, R<sub>IREF</sub> = 75 k $\Omega$  ±1% overall tolerance

|             | PARAMETER                                                                                                                                                                       | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|-----|-----|------|

| tvin_stable | When VIN is above UV_VIN_R for this duration, VIN is considered valid. If device is being powered by VBUS LDO, it will then switch to VIN supply and VBUS LDO will be disabled. |                 | 5   |     | 15  | ms   |

## 6.9 VBUS LDO Characteristics

Operating under these conditions unless otherwise noted: -10 °C  $\leq T_J \leq$  125 °C, 2.85V  $\leq V_{VIN} \leq$  5.5V,  $R_{IREF} =$  75 k $\Omega \pm$ 1% overall tolerance

| F                        | PARAMETER                   | TEST CONDITIONS                                                                                                                                                | MIN  | TYP | MAX  | UNIT |

|--------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|------|

| V_VBUS_LDO_3V            | Output voltage of VBUS LDO  | For TPS66020: VIN = 0V, VBUS ≥ 3.8V, 0 ≤ I_VBUS_LDO ≤ 30mA                                                                                                     | 3.07 | 3.3 | 3.53 | V    |

| V_VBUS_LDO_5V            | Output voltage of VBUS LDO  | For TPS66021: VIN = 0V, VBUS ≥ 5.5V, 0 ≤ I_VBUS_LDO ≤ 30mA                                                                                                     | 4.65 | 5.0 | 5.35 | V    |

| VDO_VBUS_LDO_3V          | Drop out voltage of VDD LDO | For TPS66020: VIN = 0V, VBUS<br>= 3.135 V, I_VBUS_LDO = 30 mA                                                                                                  |      |     | 0.5  | V    |

| VDO_VBUS_LDO_5V          | Drop out voltage of VDD LDO | For TPS66021: VIN= 0V, VBUS = 4.75V, I_VBUS_LDO = 30 mA                                                                                                        |      |     | 0.5  | V    |

| ILIMIT_VBUS_LDO          | Current limit VBUS LDO.     | VBUS = 5.5V, VIN= 0V, VLDO = 0V                                                                                                                                | 50   |     | 100  | mA   |

|                          |                             | For TPS66020: I_VBUS_LDO = 30mA, CVLDO = 4.7 $\mu$ F, VIN = 0V. Ramp V <sub>VBUS</sub> from 0 to 5V at $\geq$ 50V/ms. Measure from VBUS = 4.5V to VLDO = 3V.   |      |     | 1.2  | ms   |

| <sup>t</sup> en_vbus_ldo | Turn-on time of VBUS LDO.   | For TPS66021: I_VBUS_LDO = 30mA, CVLDO = 4.7 $\mu$ F, VIN = 0V. Ramp V <sub>VBUS</sub> from 0 to 7.5V at $\geq$ 50V/ms. Measure from VBUS = 7V to VLDO = 4.5V. |      |     | 1.2  | ms   |

## 6.10 Thermal Shutdown Characteristics

over operating free-air temperature range (unless otherwise noted)

|            | PARAMETER                                            | TEST CONDITIONS     | MIN | TYP | MAX | UNIT |

|------------|------------------------------------------------------|---------------------|-----|-----|-----|------|

| TSD_PP5V_R | Thermal Shutdown Temperature of the PP5V power path. | Temperature rising  | 128 | 150 | 172 | °C   |

| TSD_PP5V_F | Thermal Shutdown Temperature of the PP5V power path. | Temperature falling | 115 | 140 | 165 | °C   |

| TSDH_PP5V  | Thermal Shutdown hysteresis of the PP5V power path.  |                     |     | 10  |     | °C   |

| TSD_PPHV_R | Thermal Shutdown Temperature of the PPHV power path. | Temperature rising  | 128 | 150 | 172 | °C   |

| TSD_PPHV_F | Thermal Shutdown Temperature of the PPHV power path. | Temperature falling | 115 | 140 | 165 | °C   |

| TSDH_PPHV  | Thermal Shutdown hysteresis of the PPHV power path.  |                     |     | 10  |     | °C   |

| TSD_MAIN_R | Thermal Shutdown Temperature of the entire device.   | Temperature rising  | 140 | 160 | 178 | °C   |

| TSD_MAIN_F | Thermal Shutdown Temperature of the entire device.   | Temperature falling | 120 | 140 | 160 | °C   |

| TSDH_MAIN  | Thermal Shutdown hysteresis of the entire device.    |                     |     | 20  |     | °C   |

### 6.11 Input-output (I/O) Characteristics

Operating under these conditions unless otherwise noted: -10 °C  $\leq$  T<sub>J</sub>  $\leq$  125 °C, 2.85 V  $\leq$  V<sub>VIN</sub>  $\leq$  5.5V, R<sub>IREF</sub> = 75 k $\Omega$  ±1% overall tolerance

| F                  | PARAMETER                                                                                                                                                                                                                                                                                                                                                                                           | TEST CONDITIONS                           | MIN | TYP | MAX | UNIT |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----|-----|-----|------|

| EN_Vt+             | Positive going input-threshold voltage, % of VLDO                                                                                                                                                                                                                                                                                                                                                   | VLDO = 2.85 - 5.5V                        | 40  |     | 70  | %    |

| EN_Vt-             | Negative going input-threshold voltage, % of VLDO                                                                                                                                                                                                                                                                                                                                                   | VLDO = 2.85 - 5.5V                        | 30  |     | 60  | %    |

| EN_HYS             | Input hysteresis voltage, % of VLDO                                                                                                                                                                                                                                                                                                                                                                 | VLDO = 2.85 - 5.5V                        |     | 10  |     | %    |

| EN_RPD             | Pull-down resistance EN pin.                                                                                                                                                                                                                                                                                                                                                                        | Measured with pin voltage $V_{EN}$ = 3.3V | 500 | 650 | 800 | kΩ   |

| EN_CLAMP           | Voltage clamp on EN pin.                                                                                                                                                                                                                                                                                                                                                                            | I <sub>EN</sub> = 100 μA                  |     | 6   | 7.1 | V    |

| FLT_VOL            | Output Low Voltage, FLT pin                                                                                                                                                                                                                                                                                                                                                                         | $I_{OL} = 2mA$ , FLT driven low.          |     |     | 0.4 | V    |

| FLT_ILKG           | Leakage Current, FLT pin                                                                                                                                                                                                                                                                                                                                                                            | FLT not driven low.                       | -1  |     | 1   | μA   |

| t <sub>H_FLT</sub> | Time FLT pin remains asserted low.                                                                                                                                                                                                                                                                                                                                                                  |                                           | 4   | 10  | 16  | ms   |

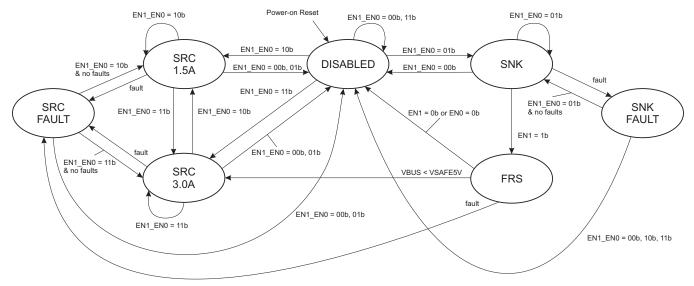

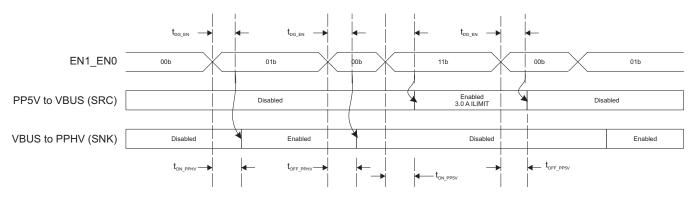

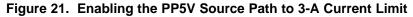

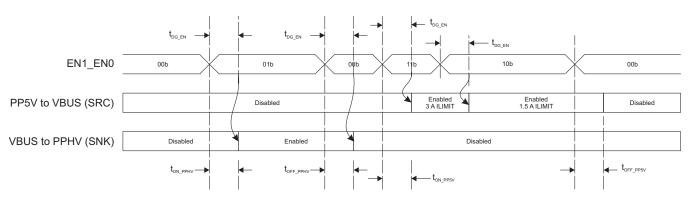

| t <sub>DG_EN</sub> | Enable deglitch filter. Pulses on<br>EN0 or EN1 < $t_{DG\_EN(MIN)}$ are<br>not propagated to the control<br>logic. Pulses on EN0 or EN1 ><br>$t_{DG\_EN(MAX)}$ are propagated to<br>the control logic. Pulses on EN0<br>or EN1 ≥ $t_{DG\_EN(MIN)}$ and ≤<br>$t_{DG\_EN(MAX)}$ may or may not<br>propagate to the control logic.<br>The filter is not applied to EN1<br>transition to the FRS state. |                                           | 78  |     | 242 | μs   |

#### 6.12 Power Consumption Characteristics

Operating under these conditions unless otherwise noted: -10 °C  $\leq$  T<sub>J</sub>  $\leq$  85 °C, 2.85V  $\leq$  V<sub>VIN</sub>  $\leq$  5.5V, R<sub>IREF</sub> = 75 k $\Omega$  ±1% overall tolerance

| PARAMETER    |                     | TEST CONDITIONS                                                                                                                                                                                                                                                                        |                    | MIN | TYP | MAX | UNIT |

|--------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-----|-----|------|

|              | Current consumed by | $\label{eq:VIN} \begin{array}{l} VIN = 3.3V, \ VBUS = 0V, \ PP5V \\ = 0V, \ PPHV = 0V, \ DISABLED \\ state. \ Measure \ I_{VIN}. \ TPS66020 \\ only. \end{array}$                                                                                                                      |                    |     | 19  | 27  | μΑ   |

| IVIN_DISABLE | VIN <sup>(1)</sup>  | $\label{eq:VIN} \begin{array}{l} \text{VIN} = 5\text{V}, \text{VBUS} = 0\text{V}, \text{PP5V} = \\ 0\text{V}, \text{PPHV} = 0\text{V}, \text{DISABLED} \\ \text{state. Measure } I_{\text{VIN}}. \text{ TPS66021} \\ \text{only.} \end{array}$                                         |                    |     | 25  | 36  | μΑ   |

|              | Current consumed by | $\label{eq:VIN} \begin{array}{l} \text{VIN} = 3.3\text{V}, \ \text{PP5V} = 5.5\text{V}, \\ \text{PPHV} = 0\text{V}, \ \text{SRC} \ 1.5\text{A} \ \text{or} \ \text{SRC} \\ 3.0\text{A} \ \text{state}. \ \text{Measure I}_{\text{VIN}}. \\ \text{TPS66020} \ \text{only}. \end{array}$ |                    |     | 136 |     | μΑ   |

| Ivin_src     | VIN <sup>(1)</sup>  | VIN = 5V, PP5V = 5.5V, PPHV<br>= 0V, SRC 1.5A or SRC 3.0A<br>state. Measure $I_{VIN}$ . TPS66021<br>only.                                                                                                                                                                              |                    |     | 214 |     | μΑ   |

|              | Current consumed by | VIN = 3.3V, PP5V = 0V, SNK state. Measure $I_{VIN}$ . TPS66020 only.                                                                                                                                                                                                                   | VBUS =<br>5.5V/22V |     | 130 |     | μΑ   |

| Ivin_snk     | VIN <sup>(1)</sup>  | VIN = 5V, PP5V = 0V, SNK state. Measure $I_{VIN}$ . TPS66021 only.                                                                                                                                                                                                                     | VBUS =<br>5.5V/22V |     | 215 |     | μΑ   |

(1) Measured with EN0 and/or EN1 set to GND or VLDO levels as required for the respective state.

# **Power Consumption Characteristics (continued)**

Operating under these conditions unless otherwise noted: -10 °C  $\leq$  T<sub>J</sub>  $\leq$  85 °C, 2.85V  $\leq$  V<sub>VIN</sub>  $\leq$  5.5V, R<sub>IREF</sub> = 75 k $\Omega$  ±1% overall tolerance

| P                     | ARAMETER                      | TEST CONDITIONS                                                                                                                                                                             | TEST CONDITIONS MIN TYP MAX |   | UNIT |     |    |

|-----------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|---|------|-----|----|

| les                   | Current consumed by           | $\label{eq:VIN} \begin{array}{l} VIN = 3.3V, \ PP5V = 5.5V, \\ PPHV = 0V, \ VBUS = 0V, \\ DISABLED \ state. \ Measure \\ I_{PP5V}. \ TPS66020 \ only. \end{array}$                          |                             |   | 2    |     | μA |

| I <sub>SD_PP5V</sub>  | PP5V <sup>(1)</sup>           | $\label{eq:VIN} \begin{array}{l} VIN = 5V, \ PP5V = 5.5V, \ PPHV \\ = 0V, \ VBUS = 0V, \ DISABLED \\ state. \ Measure \ I_{PP5V}. \ TPS66021 \\ only. \end{array}$                          |                             |   | 2    |     | μA |

|                       | Current consumed by           | $\label{eq:VIN} \begin{array}{l} VIN = 3.3V, \ PP5V = 5.5V, \\ PPHV = 0V, \ SRC \ 1.5A \ or \ SRC \\ 3.0A \ state. \ Measure \ I_{PP5V}. \\ TPS66020 \ only. \end{array}$                   |                             |   | 109  |     | μA |

| I <sub>ACT_PP5V</sub> | PP5V <sup>(1)</sup>           | $\label{eq:VIN} \begin{array}{l} VIN = 5V, PP5V = 5.5V, PPHV = \\ 0V, SRC 1.5A \mbox{ or SRC 3.0A} \\ state. \mbox{ Measure } I_{PP5V}. \mbox{ TPS66021} \\ only. \end{array}$              |                             |   | 109  |     | μA |

|                       |                               | VIN = 3.3V, PP5V = 0V, PPHV=                                                                                                                                                                | VBUS =<br>5.5V              |   | 12   | 26  | μΑ |

| I <sub>SD_VBUS</sub>  | Current consumed by           |                                                                                                                                                                                             | VBUS =<br>22V               |   | 34   |     | μΑ |

|                       | VBUS <sup>(1)</sup>           | VIN = 5V, PP5V = 0V, PPHV=<br>0V, DISABLED state. Measure                                                                                                                                   | VBUS =<br>5.5V              |   | 8    |     | μΑ |

|                       |                               |                                                                                                                                                                                             | VBUS =<br>22V               |   | 30   |     | μA |

|                       | Current consumed by           | vin = 0V, PP5V = 0V, PPHV= 5                                                                                                                                                                | VBUS =<br>5.5V              |   | 45   |     | μΑ |

| ISD_VBUS_LDO          | VBUS <sup>(1)</sup>           | 0V, DISABLED state. Measure I <sub>VBUS.</sub>                                                                                                                                              | VBUS =<br>22V               |   | 69   |     | μA |

|                       |                               | VIN = 3.3V, PP5V = 0V, SNK                                                                                                                                                                  | VBUS =<br>5.5V              | : | 325  |     | μA |

|                       | Current consumed by           | state. Measure<br>I <sub>VBUS</sub> . TPS66020 only.                                                                                                                                        | VBUS =<br>22V               | ; | 360  |     | μA |

| IACT_VBUS             | VBUS <sup>(1)</sup>           | VIN = 5V, PP5V = 0V, SNK                                                                                                                                                                    | VBUS =<br>5.5V              | ; | 342  |     | μΑ |

|                       |                               | state. Measure<br>I <sub>VBUS</sub> . TPS66021 only.                                                                                                                                        | VBUS =<br>22V               | ; | 377  |     | μΑ |

| V <sub>OC_VBUS</sub>  | Open circuit voltage,<br>VBUS | $\begin{array}{l} PP5V = 5.5V,  PPHV = 22V, \\ DISABLED \ state, \ no \ DC \ loading \\ on \ VBUS. \ Measure \ V_{\mathsf{VBUS} \ under \\ steady \ state \ conditions. \end{array}$        |                             |   |      | 0.8 | V  |

| V <sub>OC_PP5V</sub>  | Open circuit voltage,<br>PP5V | $\label{eq:VBUS} \begin{array}{l} VBUS = 22V, \ PPHV = 0V, \\ DISABLED \ state, \ no \ DC \ loading \\ on \ PP5V. \ Measure \ V_{PP5V} \ under \\ steady \ state \ conditions. \end{array}$ |                             |   |      | 0.8 | V  |

| V <sub>OC_PPHV</sub>  | Open circuit voltage,<br>PPHV | VBUS = 22V, PP5V = 0V,<br>DISABLED state, no DC loading<br>on PPHV. Measure $V_{PPHV}$ under<br>steady state conditions.                                                                    |                             |   |      | 0.8 | V  |

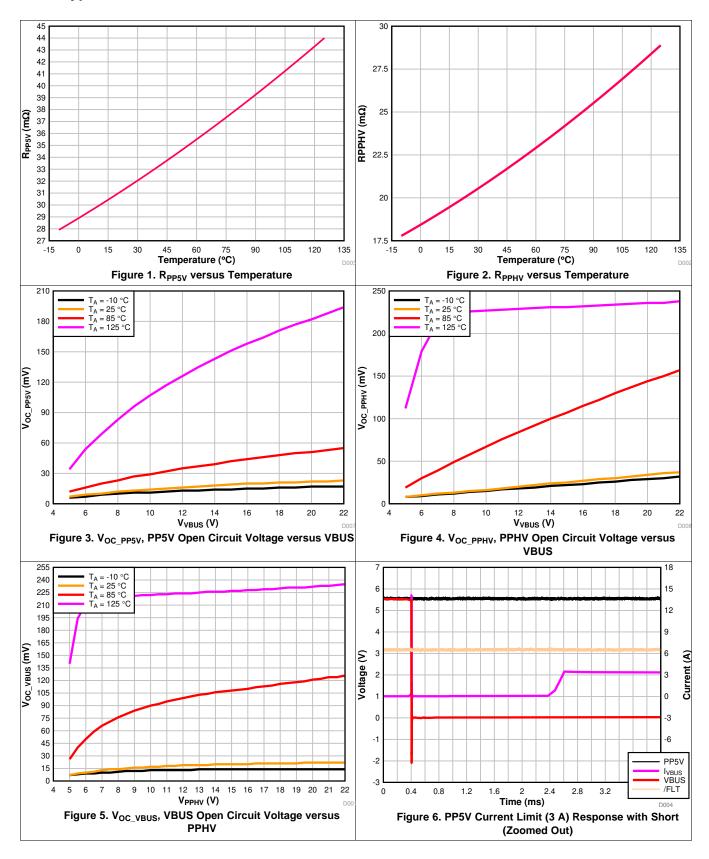

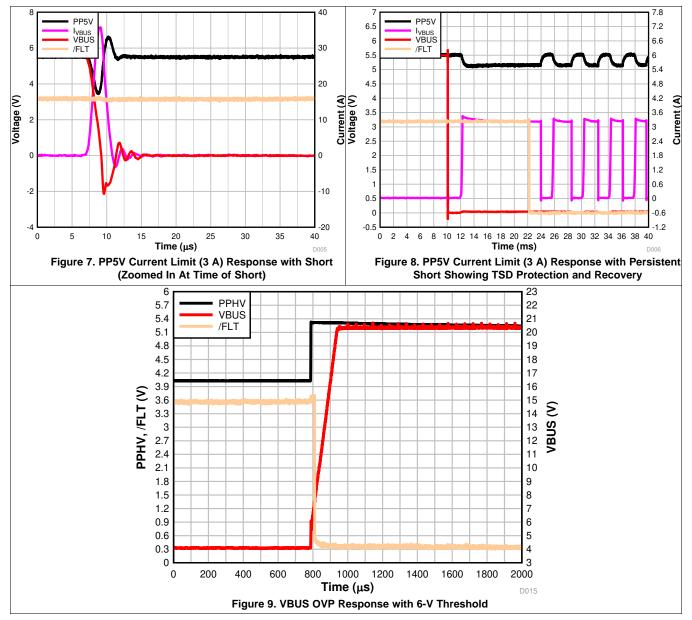

### 6.13 Typical Characteristics

Copyright © 2019, Texas Instruments Incorporated

Submit Documentation Feedback 11

### **Typical Characteristics (continued)**

#### TPS66020, TPS66021 SLVSEW8B – AUGUST 2019 – REVISED DECEMBER 2019

# 7 Parameter Measurement Information

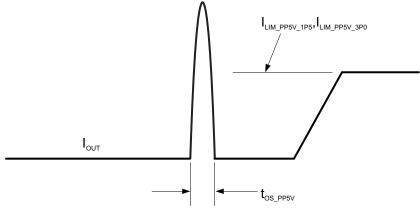

Figure 10. PP5V to VBUS Short Circuit Parameter Diagram

## 8 Detailed Description

#### 8.1 Overview

The TPS6602x is a fully featured power multiplexer with an integrated Source power path, a Sink power path, and a high voltage VBUS LDO voltage regulator. The Source power path can supply 5-V nominal power and supports two current limit settings (1.5 A or 3 A) controlled by general-purpose I/O. The Source power path includes current limit protection, overtemperature protection, reverse-current protection, undervoltage protection, and overvoltage protection. See the 5-V Source (PP5V Power Path) section. The Sink power path can support up to 5 A at 20 V controlled by general-purpose I/O. The Sink power path includes soft-start to minimize in-rush currents, overtemperature protection, reverse-current protection, undervoltage protection, and an optional overvoltage protection configured in the application. See the 20-V Sink (PPHV Power Path) section. The TPS6602x fully supports Fast Role Swap operation as specified in the Power Delivery specification. See the *Fast Role Swap (FRS)* section.

The VBUS low dropout voltage regulator may be used in systems that require power during dead battery conditions and can provide up to 30 mA to the system via the VLDO pin. Once VIN power is available, VLDO pin power is switched from the VBUS LDO regulator to the VIN pin. The TPS66020 devices VBUS LDO regulator nominally supplies 3.3 V where the TPS66021 device VBUS LDO nominally supplies 5 V. See the *Power Management and Supervisory* section.

## 8.2 Functional Block Diagram

#### 8.3 Feature Description

#### 8.3.1 5-V Source (PP5V Power Path)

The PP5V power path uses two back-to-back N-channel MOSFETs, and blocks current in both directions when the power path is disabled. The PP5V power path is a Source only path and when enabled provides power from the PP5V terminal to the VBUS terminal. The PP5V path provides up to 3-A current delivery to VBUS.

#### **Feature Description (continued)**

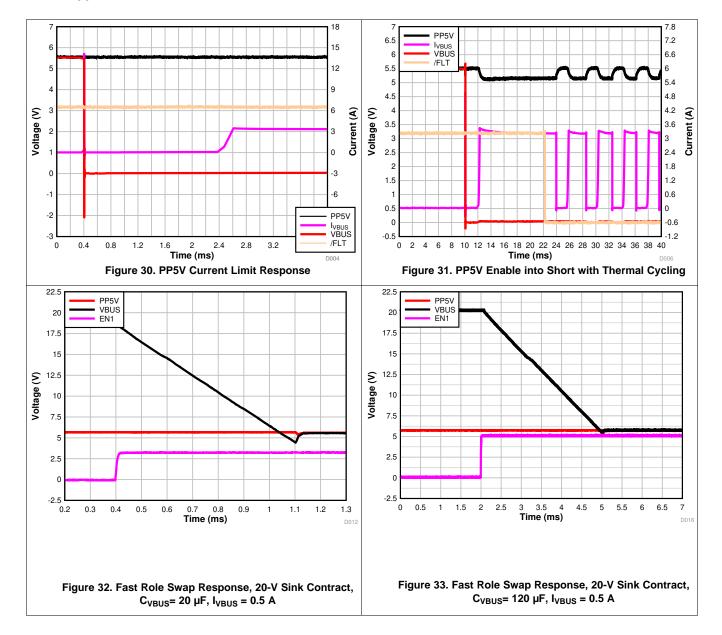

#### 8.3.1.1 PP5V Current Limit

The current through PP5V to VBUS current limit may be dynamically selected to support 1.5-A or 3-A operation via EN0 and EN1. An external resistance to GND on IREF terminal is required to set the bias current for accurate current limit operation.

Under overload conditions, the internal current-limit regulator limits the output current to the selected current limit setting,  $I_{LIM\_PP5V}$ , where  $I_{LIM\_PP5V}$  is  $I_{LIM\_PP5V\_1P5}$  or  $I_{LIM\_PP5V\_3P0}$ , as shown in the *PP5V Power Switch Characteristics* table. When an overload condition is present, the device maintains a constant output current, with the output voltage determined by ( $I_{LIM\_PP5V} \times R_{LOAD}$ ). Two possible overload conditions can occur. The first overload condition occurs when either: 1) PP5V input voltage is first applied, PP5V source path is enabled (EN1\_EN0 = 10b or EN1\_EN0 = 11b), and a short circuit is presented (load which draws  $I_{OUT} > I_{LIM\_PP5V}$ ), or 2) PP5V input voltage is present and the PP5V source path is enabled into a short circuit. The output voltage is held near zero potential with respect to ground and the TPS6602x ramps the output current to  $I_{LIM\_PP5V}$ . The TPS6602x limits the current to  $I_{LIM\_PP5V}$  until the overload condition is removed or the device begins to thermal cycle. This is demonstrated in Figure 31 where the device was enabled into a short, and subsequently cycles current off and on as the thermal protection engages.

The second condition is when an overload occurs while the PP5V source path is enabled and fully turned on. The device responds to the overload condition within time  $t_{OS\_PP5V}$  (see Figure 10) when the specified overload (per Electrical Characteristics) is applied. The response speed and shape vary with the overload level, input circuit and rate of application. The current-limit response varies between simply settling to  $I_{LIM\_PP5V}$  or turning off and a controlled return to  $I_{LIM\_PP5V}$ . Similar to the previous case, the TPS6602x limits the current to  $I_{LIM\_PP5V}$  until the overload condition is removed or the device begins to thermal cycle. The TPS6602x thermal cycles if an overload condition is present long enough to activate thermal limiting in any of the above cases. This is due to the relatively large power dissipation [( $V_{PP5V} - V_{VBUS}$ ) x  $I_{LIM\_PP5V}$ ] elevating the junction temperature. The PP5V source path turns off when its temperature reaches its thermal shutdown temperature of TSD\_PP5V\_R while in current limit. The PP5V source path remains off until its temperature cools to TSD\_PP5V\_F and then re-enables automatically.

#### 8.3.1.2 PP5V Reverse Current Protection (RCP)

When the PP5V power path is enabled, the RCP circuitry monitors the voltage across the path. If the RCP monitor detects  $V_{VBUS} - V_{PP5V} \ge V_{RCP\_THRES\_PP5V}$ , the PP5V path will be disabled preventing additional current flow from VBUS to PP5V. The power path will be completely disabled and remain disabled as long as the RCP condition persists. After the RCP event, the PP5V path will automatically re-enable. FLT is asserted when a reverse current protection event occurs on the PP5V path.

#### 8.3.2 20-V Sink (PPHV Power Path)

The PPHV path is a Sink only path, providing power from the VBUS terminal to the PPHV terminal when enabled. The PPHV power path uses two back-to-back N-channel MOSFETs, and blocks current in both directions when the power path is disabled.

#### 8.3.2.1 PPHV Soft Start

The TPS6602x PPHV power path has soft start circuitry to control in-rush current when the PPHV power path is enabled. DC loading should be minimized during soft start since the PPHV path may experience high power dissipation especially at higher VBUS voltages. This may lead to a PPHV overtemperature protection event.

#### 8.3.2.2 PPHV Reverse Current Protection (RCP)

When the PPHV power path is enabled, the RCP circuitry monitors the voltage across the path. If the RCP monitor detects  $V_{PPHV} - V_{VBUS} \ge V_{RCP_THRES_PPHV}$ , the PPHV path will be disabled preventing additional current flow from PPHV to VBUS. The power path will be completely disabled and remain disabled as long as the RCP condition persists. After the RCP event, the PPHV path will automatically re-enable. FLT is not asserted when a reverse current protection event occurs on the PPHV path.

#### Feature Description (continued)

#### 8.3.3 Overtemperature Protection

The PP5V and PPHV power paths each have an integrated temperature sensor to protect these paths from excessive heating. When the sensor in each respective path detects an overtemperature condition, the path will be automatically disabled (if enabled) and cannot be enabled until the overtemperature condition has been removed. FLT is asserted when an overtemperature event occurs.

In addition, the device has an integrated main temperature sensor. When the sensor detects an overtemperature condition, the PP5V and PPHV power paths and the VBUS LDO of the device are completely disabled until the overtemperature condition has been removed.

#### 8.3.4 VBUS Overvoltage Protection (OVP)

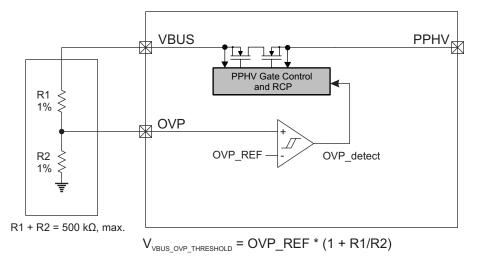

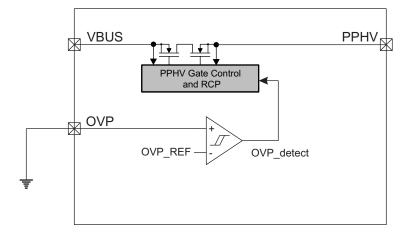

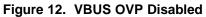

TPS6602x supports overvoltage protection on the VBUS terminal. When the voltage detected on OVP exceeds a set level, the PPHV power path will automatically be disabled (if enabled), and will remain disabled until the OVP event is removed. FLT is asserted when an overvoltage event occurs. The VBUS OVP threshold may be set using a resistor divider from VBUS to GND, whose divider output is connected to the OVP terminal as shown in Figure 11. Table 1 shows resistor divider settings for common USB Power Delivery fixed voltage supply contracts along with the resulting nominal OVP thresholds. These thresholds may be adjusted based on desired margins for a given application. If VBUS OVP is not required or needs to be disabled, the OVP terminal may be tied or driven to GND as shown in Figure 12. Lastly, as one example implementation, the OVP threshold may be controlled dynamically using outputs from a PD controller or microcontroller as shown in Figure 13. By selecting each output, different VBUS OVP threshold settings are possible.

Figure 11. VBUS OVP Threshold Set by External Resistor Divider

|                   |        |        | -                             |

|-------------------|--------|--------|-------------------------------|

| PD Fixed Contract | R1, kΩ | R2, kΩ | Nominal VBUS OVP Threshold, V |

| 5 V               | 102    | 20     | 6.1                           |

| 9 V               | 182    | 20     | 10.1                          |

| 15 V              | 309    | 20     | 16.5                          |

| 20 V              | 432    | 20     | 22.6                          |

| Table 1. | Typical | External | Resistor | Divider | Settings |

|----------|---------|----------|----------|---------|----------|

|----------|---------|----------|----------|---------|----------|

Figure 13. Selectable VBUS OVP Thresholds

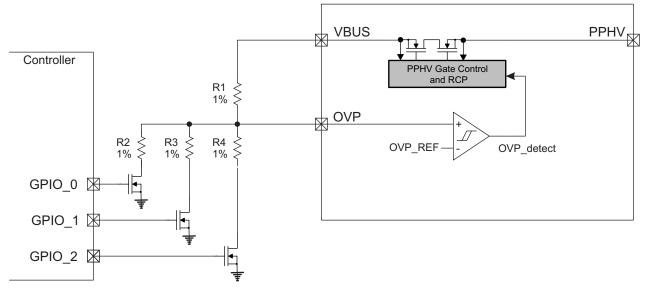

#### 8.3.5 Power Management and Supervisory

The TPS6602x Power Management block receives power from VIN or VBUS and generates voltages to provide power to the TPS6602x internal circuitry, as well as, provides power to VLDO. The power supply management and supervisory block is shown in Figure 14.

TEXAS INSTRUMENTS

www.ti.com

Figure 14. Power Management and Supervisory

The VLDO terminal may be powered from either VIN or VBUS. The normal power supply input is VIN. When VIN is present, S1 is closed and current flows from VIN to VLDO and the VBUS LDO is disabled. When VIN power is unavailable, as in a dead battery condition, the VBUS LDO will be automatically enabled when VBUS is present, and the VLDO terminal is powered by the VBUS LDO. The Switch Over Logic provides the decision making capability to choose VIN or VBUS power, depending on the state of these voltages (based on their respective UVLO comparators) and their relative levels to each other.

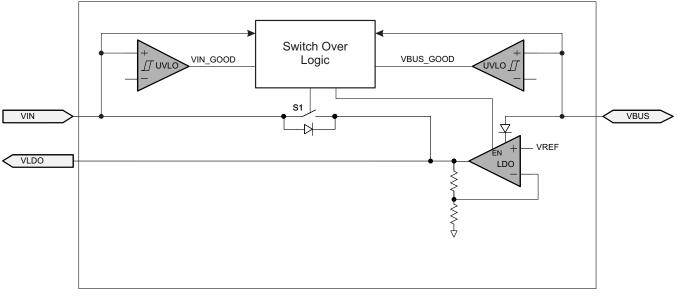

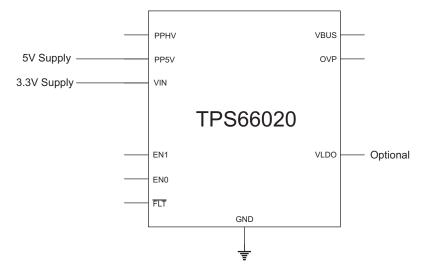

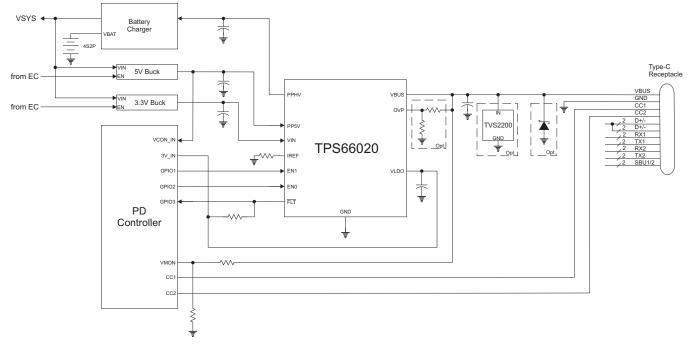

#### 8.3.5.1 Supply Connections

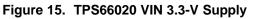

Figure 15 shows the TPS66020 VIN being supplied from a 3.3-V supply. The VLDO output may or may not be used to supply other circuitry in the application, for example a PD Controller. During a dead battery condition, the internal 3.3-V VBUS LDO provides power to the TPS66020 and the VLDO output. Once VIN input supply becomes available, the VBUS LDO is disabled and VIN provides power to the VLDO output.

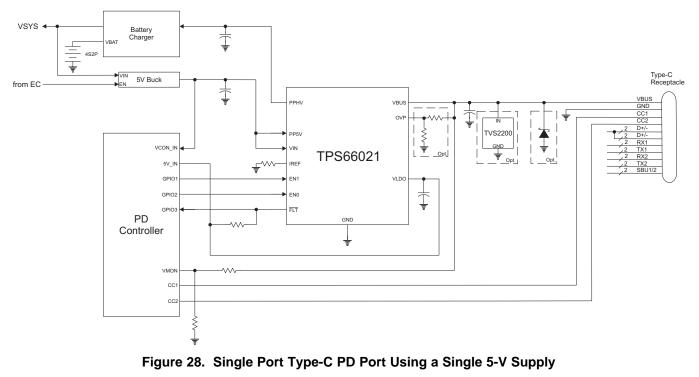

The TPS66021 is well suited for 5 V only systems. VIN of the TPS66021 may be powered from an independent supply, but in most applications it will be connected to the PP5V supply. Figure 16 shows where the VIN supply is shared with PP5V. The VLDO output may be used optionally to supply power to external circuitry. During a dead battery condition, the internal 5-V VBUS LDO provides power to the TPS66021 and the VLDO output. Once the VIN input supply, in this case PP5V, becomes available, the VBUS LDO is disabled and PP5V provides power to the VLDO output.

Figure 16. TPS66021 VIN 5-V Shared Supply

#### 8.3.5.2 Power Up Sequences

#### 8.3.5.2.1 Normal Power Up

Figure 17 shows a typical power up sequence. During normal power up, VIN supplies power to the TPS6602x. In this case, VBUS remains powered down. It is assumed a PD Controller is controlling the TPS6602x, and Sink operation is being requested.

(4)

t<sub>vin\_stable</sub>

2

3

VBUS

EN0

EN1

VIN

VLDO

VLDO Supply

Copyright © 2019, Texas Instruments Incorporated

3. VLDO supplied by VIN via switch S1. VBUS LDO remains disabled.

4. PD Controller requests Sink path to be enabled. Since VIN supply has not been above its UVLO threshold for  $t_{_{VIN,STABLE}}$ , Sink path remains disabled. In addtion, VBUS is not above its UVLO switch threshold, which also keeps the Sink path disabled.

5. VIN supply remained above its UVLO threshold for  $t_{\text{VIN}_{\text{STABLE}}}$  and VBUS is above its UVLO threshold. The Sink path enables. VBUS LDO remains disabled since VIN supply is available.

#### Figure 17. Normal Power Up Sequence

VIN switch

5)

#### 8.3.5.2.2 Dead Battery Operation

$(\mathbf{1})$

Figure 18 shows the typical power up sequence during a dead battery condition. During a dead battery condition, the TPS6602x is internally powered by the VBUS LDO. The VBUS LDO may be used to supply a limited amount of current for use in the system during dead battery, such as supplying power to a PD controller. In this case, it is assumed the VLDO terminal is providing power to a PD controller that is controlling the TPS6602x. Once VIN is stable, the VLDO terminal switches from being supplied by the VBUS LDO to being supplied by the VIN terminal, and the VBUS LDO is automatically disabled. The switch over process is completely seamless.

#### NOTE

Switching from VBUS LDO operation to VIN operation is seamless and no device reset will occur. When switching from VIN power to VBUS LDO operation, the switch over circuitry will attempt to switch over to the VBUS LDO, however it is not assured that the VLDO level will be maintained above the VLDO UVLO threshold. In this case, a device reset may or may not occur.

| VBUS        |                         | <ul> <li>Device is in dead battery condition. PD<br/>controller advertises as a Sink. Upon<br/>connection to a Source, VBUS begins to rise.</li> </ul>                       |

|-------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EN0         | 3                       | 2. VBUS LDO is selected by the power management logic and VLDO begins to rise.                                                                                               |

| EN1         |                         | 3. PD Controller negotiates a contract (may be                                                                                                                               |

| VIN         |                         | 5V or higher) and asserts EN0 to turn on the PPHV Sink path in order to charge the system.                                                                                   |

| VLDO        |                         | <ul> <li>4. System begins to charge and VIN begins to<br/>rise. VIN passes its UVLO threshold.</li> </ul>                                                                    |

| /LDO Supply | 2 VBUS LDO 5 VIN switch | 5. If VIN supply remains above its UVLO<br>threshold for t <sub>VIN_STABLE</sub> , VBUS LDO is disabled<br>and VLDO is switched over to be supplied by<br>VIN via switch S1. |

#### Figure 18. Dead Battery Power Up Sequence

Product Folder Links: TPS66020 TPS66021

www.ti.com

#### 8.4 Device Functional Modes

#### 8.4.1 State Transitions

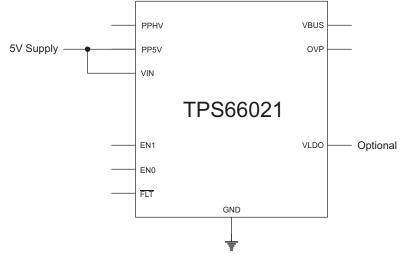

EN0 and EN1 are used by the application to control the state of the device. Figure 19 shows the supported state transitions.

Figure 19. TPS6602x Functional State Diagram

#### 8.4.1.1 DISABLED State

In the DISABLED state, EN1 = 0, EN0 = 0. While in the DISABLED state:

- PP5V power path is disabled

- PP5V current limit, overvoltage, overtemperature, and reverse current protections are disabled

- PPHV power path is disabled

- PPHV overtemperature, reverse-current, and VBUS overvoltage protections are disabled

- VIN and VBUS undervoltage lockout are enabled

The following transitions are possible from the DISABLED state:

- SRC 1.5-A state if (EN1 = 1) and (EN0 = 0) and (PP5V UVLO event not detected) and (PPHV path is completely off)

- SRC 3.0-A state if (EN1 = 1) and (EN0 = 1) and (PP5V UVLO event not detected) and (PPHV path is completely off)

- SNK state if (EN1 = 0) and (EN0 = 1) and (VBUS UVLO event not detected) and (PP5V is completely off)

#### 8.4.1.2 SRC 1.5-A State

In the SRC 1.5-A state, EN1 = 1, EN0 = 0. While in the SRC 1.5-A state:

- PP5V power path is enabled with current limit set to I<sub>LIM\_PP5V\_1P5</sub>

- PP5V overvoltage, overtemperature and reverse current protections are enabled

- PPHV power path is disabled

- PPHV overtemperature, reverse-current and VBUS overvoltage protections are disabled

- VIN and PP5V undervoltage lockout are enabled

The following transitions are possible from the SRC 1.5-A state:

- SRC 3-A state if (EN1 = 1) and (EN0 = 1)

- DISABLED state if:

- (EN1 = 0) and (EN0 = 0) -or-

- (EN1 = 0) and (EN0 = 1)

### **Device Functional Modes (continued)**

- SRC FAULT state if:

- PP5V UVLO, PP5V OVP, or PP5V RCP event detected -or-

- PP5V current limit and PP5V TSD events detected

### 8.4.1.3 SRC 3-A State

In the SRC 3-A state, EN1 = 1, EN0 = 1. While in the SRC 3-A state:

- PP5V power path is enabled with current limit set to I<sub>LIM\_PP5V\_3P0</sub>

- PP5V overvoltage, overtemperature and reverse current protections are enabled

- PPHV power path is disabled

- PPHV overtemperature, reverse-current, and VBUS overvoltage protections are disabled

- VIN and PP5V undervoltage lockout are enabled

The following transitions are possible from the SRC 3-A state:

- SRC 1.5-A state if (EN1 = 1) and (EN0 = 0)

- DISABLED state if:

- (EN1 = 0) and (EN0 = 0) -or-

- (EN1 = 0) and (EN0 = 1)

- SRC FAULT state if:

- PP5V UVLO, PP5V OVP, or PP5V RCP event detected -or-

- PP5V current limit and PP5V TSD events detected

### 8.4.1.4 SNK State

In the SNK state, EN1 = 0, EN0 = 1. While in the SNK state:

- PP5V power path is disabled

- PP5V overvoltage, overtemperature and reverse current protections are disabled

- PPHV power path is enabled

- PPHV overtemperature, VBUS overvoltage (if OVP terminal not grounded) and reverse-current protections are enabled

- VIN and VBUS undervoltage lockout are enabled

The following transitions are possible from the SNK state:

- FRS (Fast Role Swap) state

- DISABLED state if:

- (EN1 = 0) and (EN0 = 0)

- SNK FAULT state if:

- VBUS OVP (if OVP terminal not grounded) event detected -or-

- PPHV TSD event detected

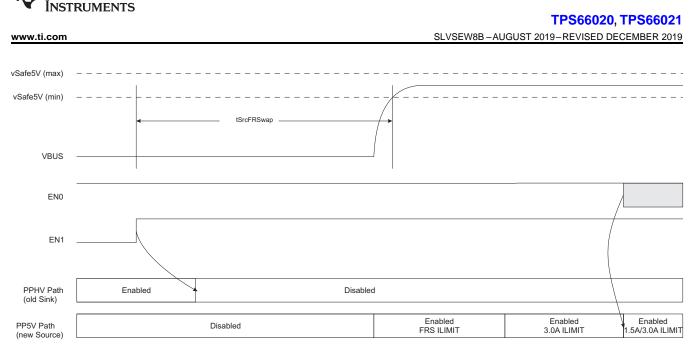

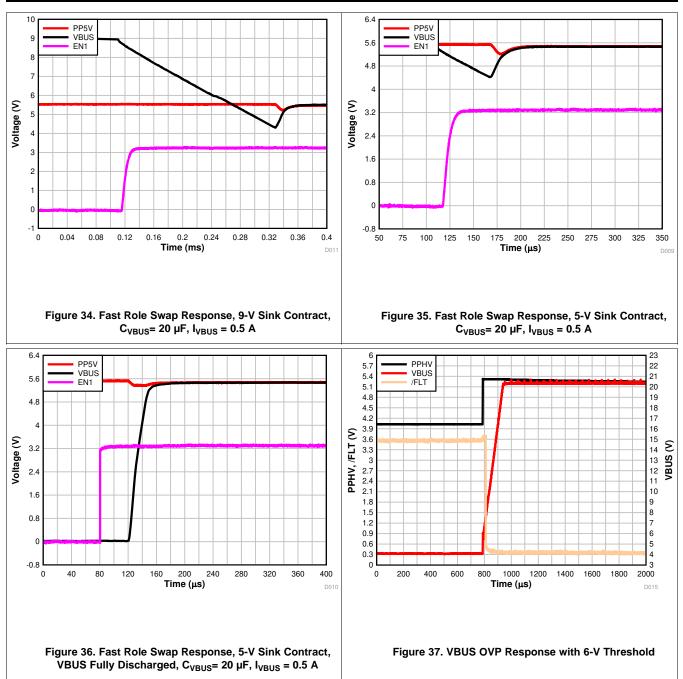

#### 8.4.1.5 FRS (Fast Role Swap) State

In the FRS state, EN1 = 1, EN0 = 1. The FRS state is a transitional state, that transitions automatically from the SNK state to the SRC 3-A state upon successful completion of the fast role swap sequence:

- PPHV power path is automatically disabled

- PPHV overtemperature, VBUS overvoltage (if OVP terminal not grounded) protections are disabled

- VIN and PP5V undervoltage lockout are enabled

- PP5V power path is automatically enabled along with its overvoltage, overtemperature and RCP protection circuits upon successfully completing the fast role swap sequence.

The following transitions are possible from the FRS state:

- SRC 3-A state. This transition is automatic upon successful completion of the fast role swap sequence.

- DISABLED state if:

- (EN1 = 0) or (EN0 = 0). This may allow for exiting a FRS sequence depending on the current status of the

### **Device Functional Modes (continued)**

- FRS sequence.

- SRC FAULT state if:

- PP5V UVLO, PP5V OVP event detected -or-

- PP5V current limit and PP5V TSD events detected

### 8.4.2 SRC FAULT State

The SRC FAULT state is entered when any PP5V fault event is detected. Upon entering the SRC FAULT state, the PP5V power path is disabled. The following transitions are possible from the SRC FAULT state:

- DISABLED state if:

- (EN1 = 0) and (EN0 = 0) -or-

- (EN1 = 0) and (EN0 = 1)

- SRC 1.5-A state if:

- (EN1 = 1) and (EN0 = 0) -and-

- PP5V TSD, PP5V OVP, PP5V RCP, PP5V UVLO, and PP5V current limit events are not detected.

- SRC 3-A state if:

- (EN1 = 1) and (EN0 = 1) -and-

- PP5V TSD, PP5V OVP, PP5V RCP, PP5V UVLO, and PP5V current limit events are not detected.

#### 8.4.3 SNK FAULT State

The SNK FAULT state is entered when any PPHV fault event is detected. Upon entering the SNK FAULT state, the PPHV power path is disabled. The following transitions are possible from the SNK FAULT state:

- DISABLED state if:

- (EN1 = 1) or (EN0 = 0)

- SNK state if:

- (EN1 = 0) and (EN0 = 1) -and-

- PPHV TSD, VBUS OVP (if OVP terminal not grounded) events are not detected

#### 8.4.4 Device Functional Mode Summary

Table 2 summarizes the functional modes for the TPS6602x. As shown, the enabling and disabling of the respective Source or Sink is dependent upon the voltages present on PP5V and VBUS, as well as, the EN0 and EN1 control signals.

## **Device Functional Modes (continued)**

| EN1 | EN0 | VIN      | V <sub>VBUS</sub> | V <sub>PP5V</sub> | FLT  | Device State | Source Path                                    | Sink Path                                    |

|-----|-----|----------|-------------------|-------------------|------|--------------|------------------------------------------------|----------------------------------------------|

| 0   | 0   | ≥ UV_VIN | x                 | х                 | Hi-Z | DISABLED     | Disabled<br>Safety engaged.                    | Disabled<br>Safety engaged.                  |

|     |     |          |                   | ≥UV PP5V          | Hi-Z | SRC 1.5 A    | Enabled<br>RCP, OVT, ILIM 1.5-A<br>enabled.    | Disabled<br>Safety engaged.                  |

| 1   | 0   | ≥ UV_VIN | х                 | 200_FF30          | L    | SRC FAULT    | Disabled<br>OVP, OVT, ILIMIT, or<br>RCP event. | Disabled<br>Safety engaged.                  |

|     |     |          |                   | < UV_PP5V         | L    | SRC FAULT    | Disabled<br>PP5V UVLO event.                   | Disabled<br>Safety engaged.                  |

|     |     |          |                   | ≥UV PP5V          | Hi-Z | SRC 3 A      | Enabled<br>RCP, OVT, ILIM 3-A<br>enabled.      | Disabled<br>Safety engaged.                  |

| 1   | 1   | ≥ UV_VIN | x                 | 2 UV_FF3V         | L    | SRC FAULT    | Disabled<br>OVP, OVT, ILIMIT, or<br>RCP event. | Disabled<br>Safety engaged.                  |

|     |     |          |                   | < UV_PP5V         | L    | SRC FAULT    | Disabled<br>PP5V UVLO event.                   | Disabled<br>Safety engaged.                  |

|     |     | ≥ UV_VIN | ≥ UV_VBUS         | х                 | Hi-Z | SNK          | Disabled<br>Safety engaged.                    | Enabled<br>RCP, OVT enabled                  |

| 0   | 1   |          |                   | х                 | Hi-Z | SNK FAULT    | Disabled<br>Safety engaged.                    | Enabled with Blocking<br>RCP event.          |

| 0   | I   |          |                   | х                 | L    | SNK FAULT    | Disabled<br>Safety engaged.                    | Disabled<br>OVP <sup>(2)</sup> or OVT event. |

|     |     |          | < UV_VBUS         | х                 | Hi-Z | SNK FAULT    | Disabled<br>Safety engaged.                    | Disabled<br>VBUS UVLO event.                 |

|     |     |          | ≥ vSafe5V         | ≥ UV_PP5V         | Hi-Z | FRS          | Disabled<br>OVT, ILIM 3-A enabled              | Disabled<br>Safety engaged.                  |

| 1   | 1   | ≥ UV_VIN |                   | ≥ UV_PP5V         | Hi-Z | SRC 3 A      | Enabled<br>RCP, OVT, ILIM 3-A<br>enabled       | Disabled<br>Safety engaged.                  |

|     |     |          | < vSafe5V         | ≥ UV_PP5V         | L    | SRC FAULT    | Disabled<br>OVP, OVT, ILIMIT, or<br>RCP event. | Disabled<br>Safety engaged.                  |

|     |     |          |                   | < UV_PP5V         | L    | SRC FAULT    | Disabled<br>PP5V UVLO event.                   | Disabled<br>Safety engaged.                  |

| х   | х   | < UV_VIN | < UV_VBUS         | х                 | Hi-Z | DISABLED     | Disabled<br>Safety engaged.                    | Disabled<br>Safety engaged.                  |

| 0   | 0   | < UV_VIN | ≥ UV_VBUS         | х                 | Hi-Z | DISABLED     | Disabled<br>Safety engaged.                    | Disabled<br>Safety engaged.                  |

| 1   | 0   | < UV_VIN | ≥ UV_VBUS         | ≥ UV_PP5V         | L    | SRC FAULT    | Disabled<br>RCP, OVT, ILIM 1.5A<br>enabled     | Disabled<br>Safety engaged.                  |

| 1   | 1   | < UV_VIN | ≥ UV_VBUS         | ≥ UV_PP5V         | L    | SRC FAULT    | Disabled<br>RCP, OVT, ILIM 3A<br>enabled       | Disabled<br>Safety engaged.                  |

(1) X: do-not-care.

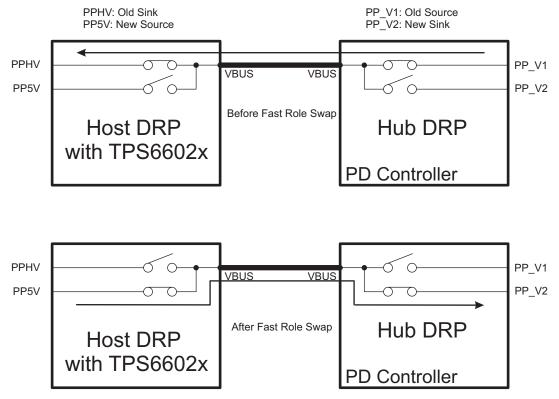

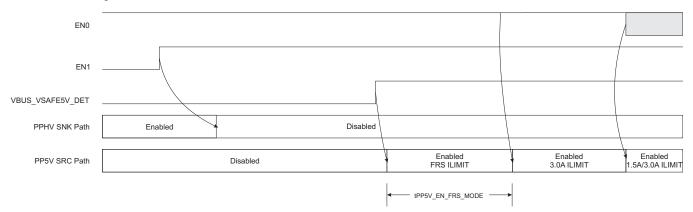

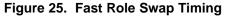

(1) A do not out?