TPIC7218-Q1

SLDS182A - AUGUST 2010-REVISED JULY 2015

# TPIC7218-Q1 Power Controller and Sensor ASIC For Braking Applications

#### 1 Device Overview

#### 1.1 Features

- Qualified for Automotive Applications

- AEC-Q100 Qualified with the Following Results:

- Device Temperature Grade 1: –40°C to 125°C

Ambient Operating Temperature Range

- Device HBM ESD Classification Level 2

- Device CDM ESD Classification Level C4

- · PWM Low-Side Drivers

- 4 PWM Low-Side Driver Outputs

- Current Limitation

- Thermal Protection: T<sub>J</sub> = 185°C (Minimum)

- Open-Load Detection

- Energy Capability: 30 mJ at T<sub>J</sub> = 150°C

- Clamp Voltage: 40 V

- Low  $R_{DSon}$ : 0.3  $\Omega$  (Maximum) at  $T_J = 150$ °C

- · Digital Low-Side Drivers

- 4 Digital Low-Side Driver Outputs

- Current Limitation

- Thermal Protection: T<sub>J</sub> = 185°C (Minimum)

- Open-Load Detection

- Energy Capability: 50 mJ at T<sub>J</sub> = 150°C

- Clamp Voltage: 40 V

- Low  $R_{DSon}$ : 0.2  $\Omega$  (Maximum) at  $T_J = 150$ °C

- · Dual High-Side Power Drivers

- Direct Input Control

- PWM Capability

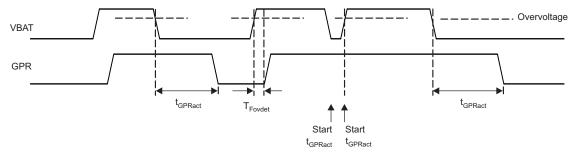

- Load Dump (overvoltage) Detection

- Programmable overcurrent detection

- Load Leakage Detection

- Programmable short-circuit Protection

- Fault detection over SPI

#### 1.2 Applications

Anti-lock Braking Systems (ABS)

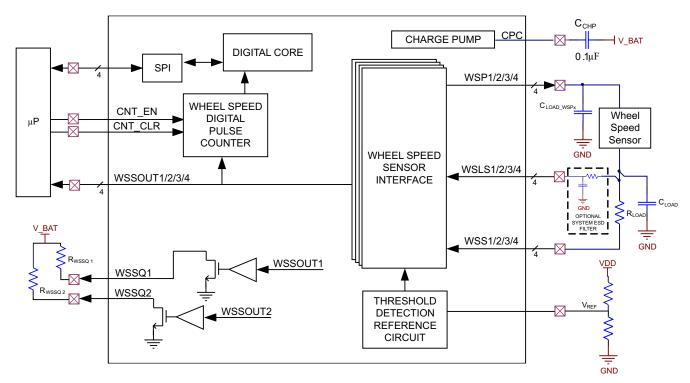

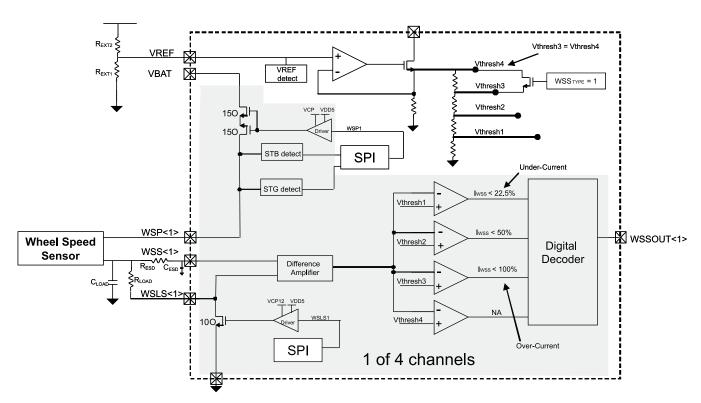

- Wheel-Speed Sensor Interface

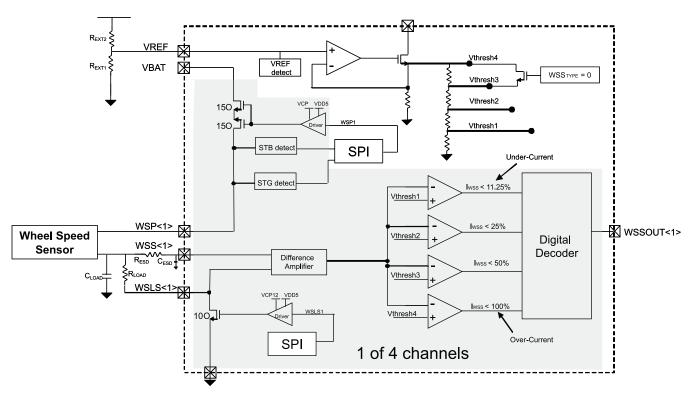

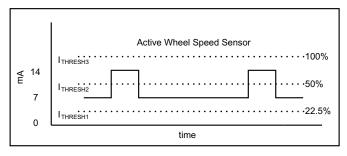

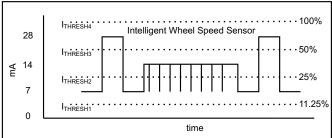

- Compatible with Intelligent and Active Wheel-Speed Sensors

- 4 High-Side Switches With Short-Circuit Protection

- 4 Low-Side Switches With Short-Circuit Protection

- 2 High Voltage Low-Side Output Drivers

- 4 Digital Outputs to Indicate the Speed

- Integrated Data Decoder for Intelligent Wheel-Speed Sensors

- Open-Drain Warning Lamp Drivers

- 2 High Voltage Drivers

- Thermal Protection With Hysteresis

- Current Limitation

- T<sub>J</sub> = 185°C (Minimum)

- $R_{DSon}$ : 4  $\Omega$  at  $T_J$  = 150°C

- Clamp Voltage: 40 V

- · Other Features

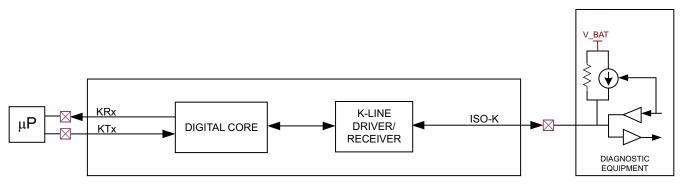

- K-LINE Transceiver

- 3.3-V or 5-V Compatible Digital IO

- Internal 3.3-V Regulator

- Internal Charge Pump

- 1 Low-Voltage Open-Drain Warning Lamp Driver

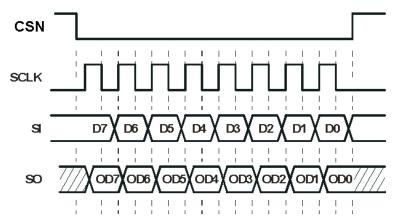

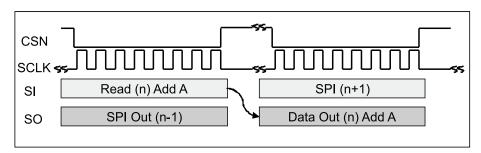

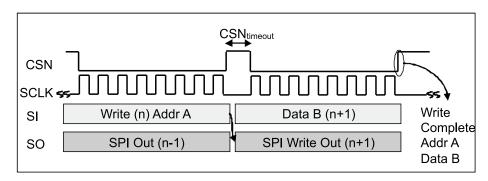

- Full Duplex SPI Interface

- Watchdog Input With Open-Drain Fault Reporting for Safety

- Pb-Free ASIC

- Compliant With CISPR 25 NB Class 5 for Conducted and Radiated Emissions

Electronic Stability Control Systems (ESC)

#### 1.3 Description

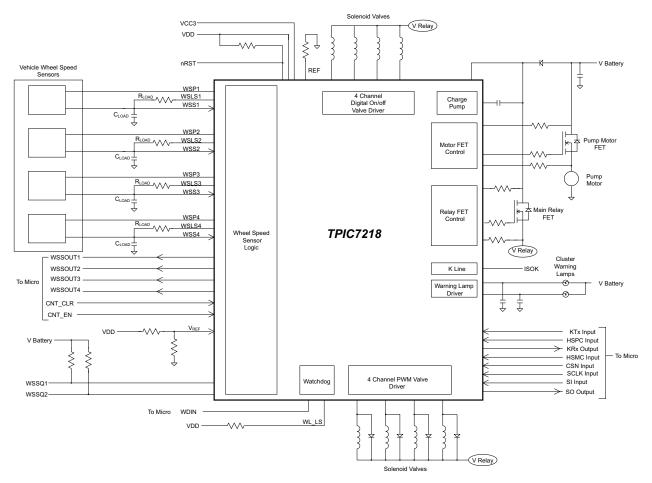

The TPIC7218-Q1 device integrates in single package several functions needed in ABS and ESC electronic control units (ECU). This integration coupled with the minimization of the external components saves valuable ECU board space.

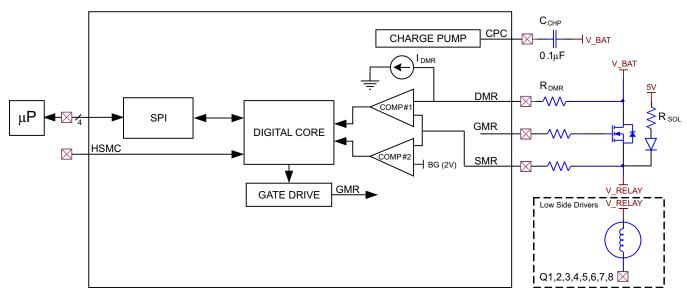

The TPIC7218-Q1 device is an antilock braking controller capable of directly driving eight solenoid valves with internal high-current low-side drivers. Low-side drivers configured for digital control do not require external voltage clamps. The TPIC7218-Q1 device has gate drive capability for two high-side N-Channel MOSFETs that can be used to drive a pump motor and power to all solenoids. The TPIC7218-Q1 device provides a fault-tolerant interface for both Intelligent and Active wheel-speed sensors to an external microprocessor. The TPIC7218-Q1 device can be used with either 3.3- or 5-V microprocessors and uses a standard SPI (Serial-Peripheral Interface).

The TPIC7218-Q1 device has two internal open-drain warning lamp drivers that can be pulled up to battery voltage, as well as one low-voltage driver. An internal state machine monitors a watchdog input and reports faults on a warning-lamp pin and SPI register. A K-Line transceiver is also included. A multitude of safety and fault monitoring functionality supervise both system and TPIC7218-Q1 circuits. Faults must be polled and reset over SPI. The TPIC7218-Q1 device is designed for use in harsh automotive environments, capable of withstanding high operating temperatures and electrically noisy signals and power. Short-to-ground, short-to-battery, and open-load conditions are tolerated and monitored. The TPIC7218-Q1 device also exhibits outstanding Electro-Magnetic Compatibility (EMC) performance.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)     |  |

|-------------|------------|---------------------|--|

| TPIC7218-Q1 | HTQFP (80) | 12.00 mm × 12.00 mm |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

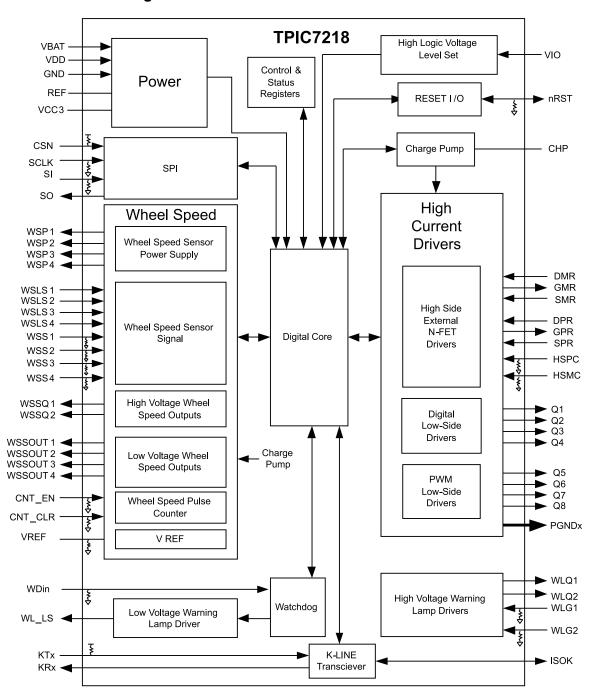

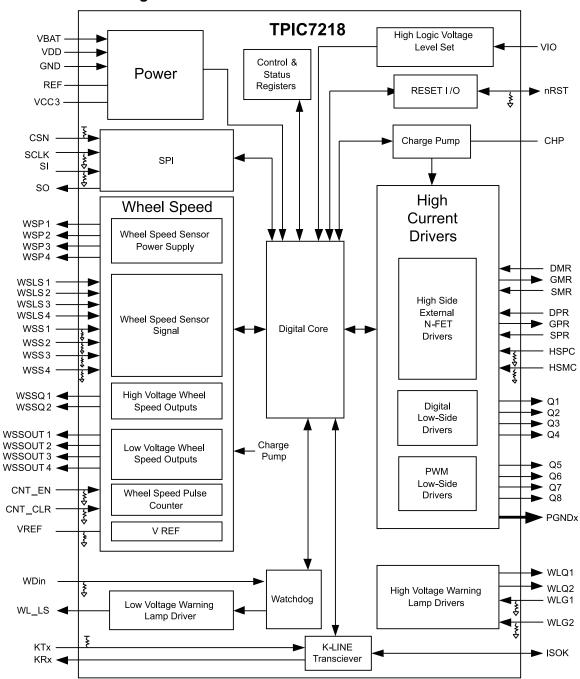

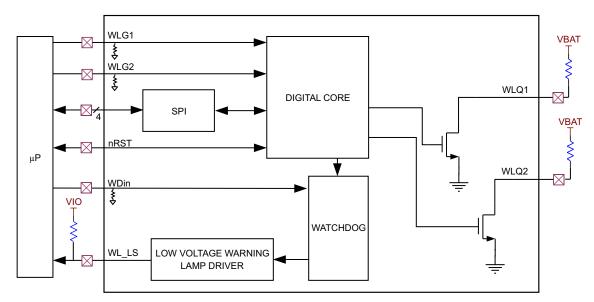

#### 1.4 Functional Block Diagram

Figure 1-1. Functional Block Diagram

Page

## Table of Contents

| 2        | Rev        | rision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |    |              |                                                                                        |            |

|----------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----|--------------|----------------------------------------------------------------------------------------|------------|

|          | T          | Signal 2511 State Street Street, Stree |   |    | Infor        | mation                                                                                 | 57         |

|          | 4.22       | Digital Low-Side Driver Switching Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   | 10 |              | hanical, Packaging, and Orderable                                                      |            |

|          | 4.21       | HS Driver Switching Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |    | 9.5          | Glossary                                                                               | 5          |

|          | 4.20       | Wheel-Speed Counter Switching Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |    | 9.4          | Electrostatic Discharge Caution                                                        | 5          |

|          | 4.19       | Power Supply Switching Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |    | 9.3          | Trademarks                                                                             | 56         |

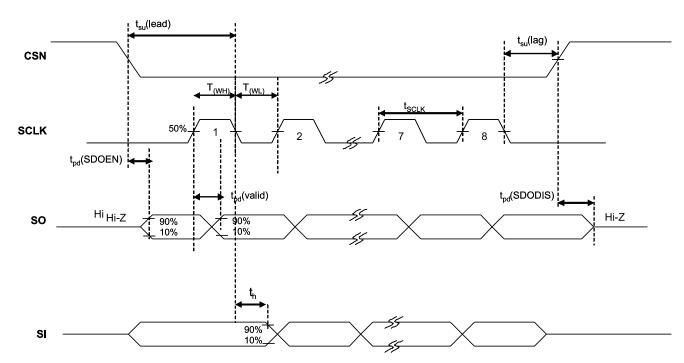

|          | 4.18       | SPI Timing Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _ |    | 9.2          | Community Resources                                                                    | 56         |

|          | 4.17       | RST Output Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |    | 9.1          | Documentation Support                                                                  | 56         |

|          | 4.16       | Wheel-Speed Output Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _ | 9  | Devi         | ce and Documentation Support                                                           | 56         |

|          | 4.15       | Wheel-Speed Low-Side Driver Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |    | 8.2          | Layout Example                                                                         | 52         |

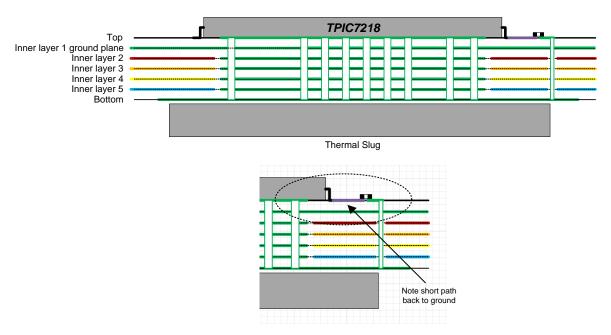

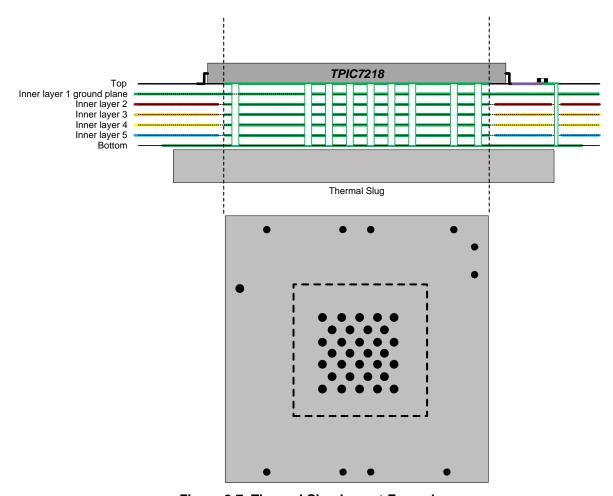

|          | 4.14       | Wheel-Speed High-Side Driver Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |    | 8.1          | Layout Guidelines                                                                      | <u>5</u> ( |

|          | 4.13       | WL_LS Low-Side Switch Output Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _ | 8  | Layo         | out                                                                                    | 50         |

|          | 4.12       | SPI Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | _ | 7  | Powe         | er Supply Recommendations                                                              | 50         |

|          | 4.11       | Power Supply Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _ |    | 6.2          | Typical Application                                                                    | 4          |

|          | 4.10       | Warning Lamp Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _ |    | 6.1          | Application Information                                                                | 47         |

|          | 4.9        | K-Line Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   | 6  | Appl         | lication and Implementation                                                            |            |

|          | 4.8        | High-Side Driver Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |    | 5.6          | Register Maps                                                                          | 4          |

|          | 4.7        | Digital Low-Side Driver Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |    | 5.5          | Programming                                                                            |            |

|          | 4.6        | PWM Low-Side Driver Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | _ |    | 5.4          | Device Functional Modes                                                                | _          |

|          | 4.4<br>4.5 | Input Port Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _ |    | 5.3          | Feature Description                                                                    |            |

|          | 4.3<br>4.4 | Thermal Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _ |    | 5.2          | Functional Block Diagram                                                               |            |

|          | 4.2        | Recommended Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | _ |    | 5.1          | Overview                                                                               |            |

|          | 4.1        | ESD Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _ | 5  | Deta         | iled Description                                                                       | _          |

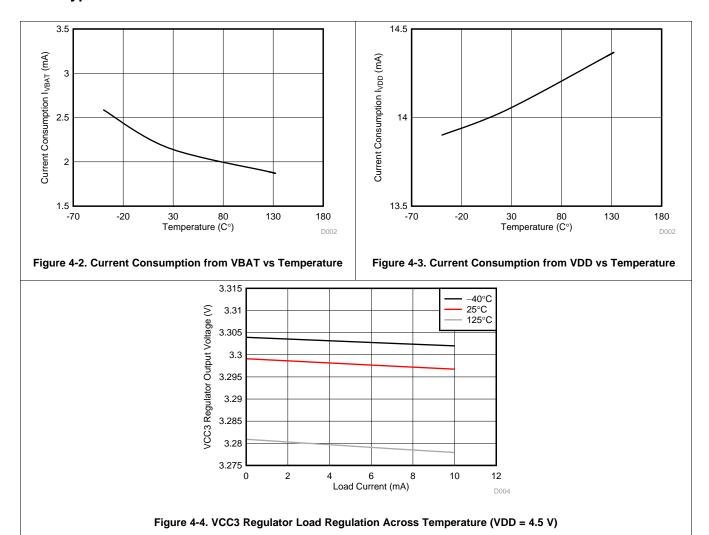

| •        | 4.1        | Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | _ |    | 4.30         | Typical Characteristics                                                                |            |

| ,<br>1   |            | ifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _ |    | 4.29         | Wheel-Speed Output Switching Characteristics                                           | 16         |

| <u> </u> |            | sion History Configuration and Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | _ |    | 4.20         | Characteristics                                                                        | 16         |

| ,        | 1.4        | Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | _ |    | 4.27<br>4.28 | Wheel Speed Interface Switching Characteristics Wheel-Speed High-Side Driver Switching | 10         |

|          | 1.3        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _ |    | 4.26         | Wheel Speed Interfees Switching Characteristics                                        |            |

|          | 1.2        | Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _ |    | 4.25         | Warning Lamp Switching Characteristics                                                 |            |

|          | 1.1        | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | _ |    | 4.24         | K-Line Switching Characteristics                                                       |            |

| ı        |            | ce Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _ |    | 4.23         | PWM Low-Side Driver Switching Characteristics                                          |            |

|          |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4 |    |              |                                                                                        |            |

# Changes from Original (August 2010) to Revision A

Released full version of the data sheet .....

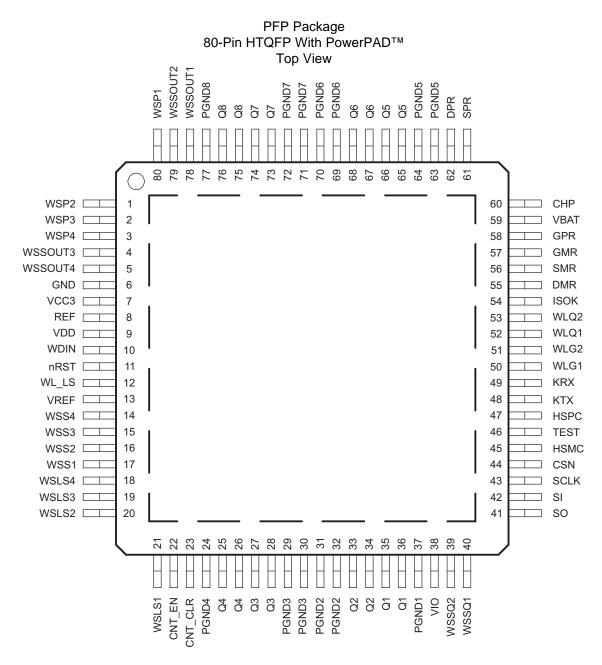

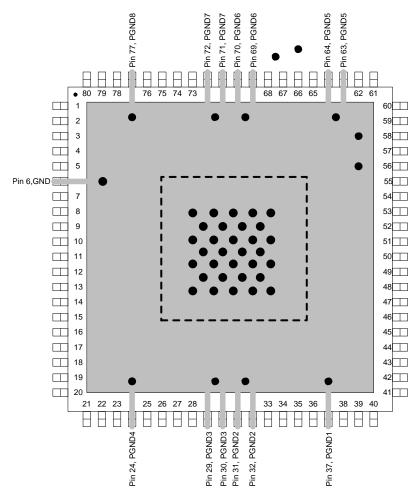

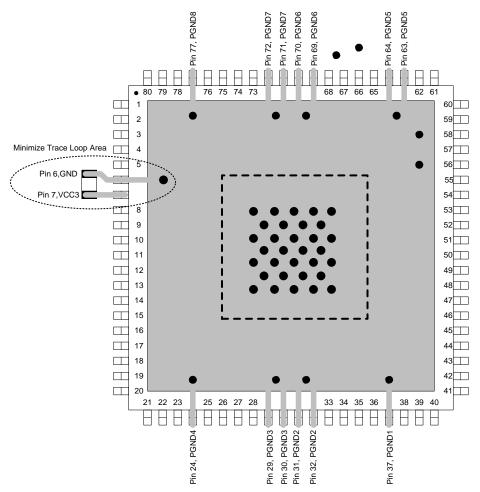

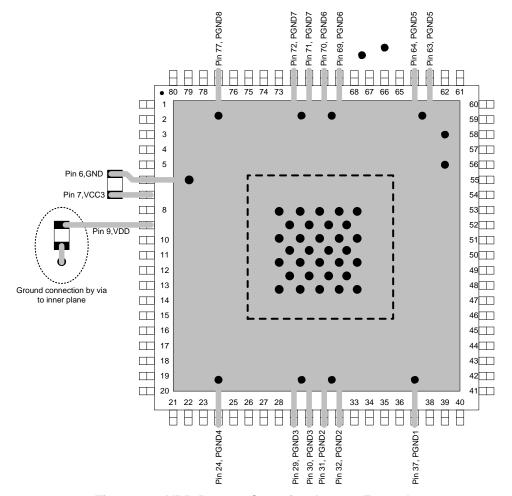

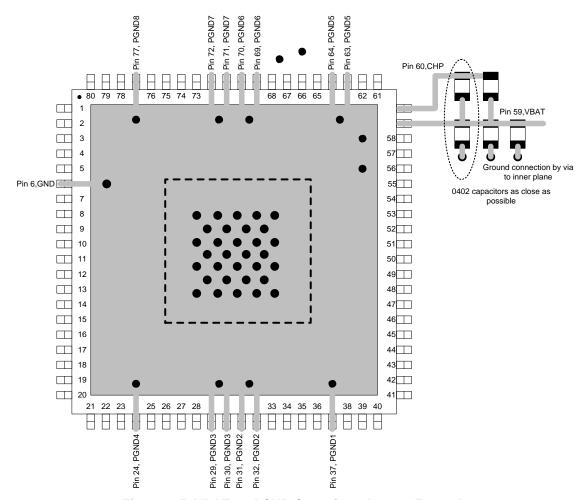

## 3 Pin Configuration and Functions

#### **Pin Functions**

| PIN     |     |     |                                                                                                            |                       | PIN DURING                      |

|---------|-----|-----|------------------------------------------------------------------------------------------------------------|-----------------------|---------------------------------|

| NAME    | NO. | I/O | FUNCTION DESCRIPTION                                                                                       | PULLUP OR<br>PULLDOWN | RESET<br>CONDITION              |

| СНР     | 60  | 0   | External 100-nF capacitor to VBAT for an internal charge pump                                              | Pullup                | VCHP = VBAT +<br>12 V (typical) |

| CNT_CLR | 23  | 1   | Clear bit for the 8-bit digital counter that counts the wheel-<br>speed sensor pulse edges seen in WSSOUTx | Pulldown              |                                 |

| CNT_EN  | 22  | 1   | Enable bit for the 8-bit digital counter that counts the wheel-speed sensor pulse edges seen in WSSOUTx    | Pulldown              |                                 |

| CSN     | 44  | I   | SPI chip select active low pin                                                                             | Pullup                |                                 |

## Pin Functions (continued)

| PII        | N                                 |        | Fin Functions (continued)                                                                                         | INPUT PIN       | PIN DURING                         |

|------------|-----------------------------------|--------|-------------------------------------------------------------------------------------------------------------------|-----------------|------------------------------------|

| NAME       | NAME NO. I/O FUNCTION DESCRIPTION |        | PULLUP OR<br>PULLDOWN                                                                                             | RESET CONDITION |                                    |

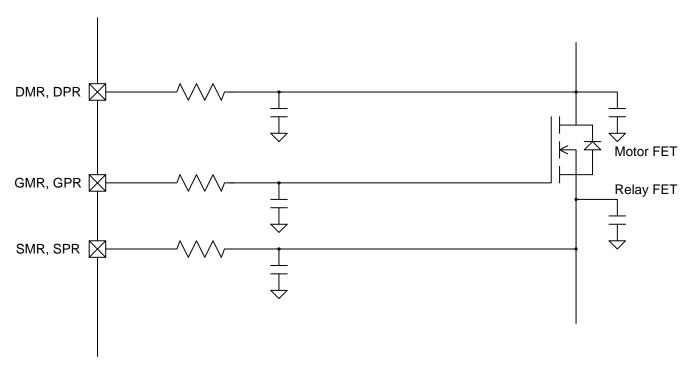

| DMR        | 55                                | I      | Drain pin for master relay (MR) FET                                                                               | Pulldown        | Externally supplied voltage (VBAT) |

| DPR        | 62                                | I      | Drain pin for PR (pump motor relay) FET                                                                           | Pulldown        | Externally supplied voltage (VBAT) |

| GMR        | 57                                | 0      | Gate pin for master relay (MR) FET                                                                                |                 | Low                                |

| GND        | 6                                 | Ground | Ground                                                                                                            |                 |                                    |

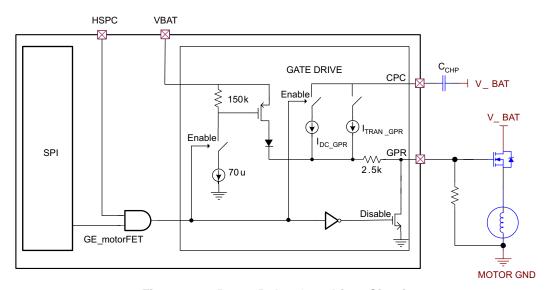

| GPR        | 58                                | 0      | Gate pin for PR (pump motor relay) FET                                                                            |                 | Low                                |

| HSMC       | 45                                | I      | Logic input for MR (master relay) FET                                                                             | Pulldown        |                                    |

| HSPC       | 47                                | In     | Logic input for PR (pump motor relay) FET                                                                         | Pulldown        |                                    |

| ISOK       | 54                                | I/O    | K-line serial data transmit output to diagnosis tester and K-line serial data receive input from diagnosis tester | High-Z          | High-Z                             |

| KRx        | 49                                | 0      | K-line serial data input to the microcontroller                                                                   |                 | High                               |