Keywords: PRM, HDLC

# APPLICATION NOTE 6505 HANDLING PERFORMANCE REPORT MESSAGES IN THE DS2155

By: Aparna K P

Abstract: This application note discusses transmitting/receiving a PRM as an HDLC message over T1 FDL and time slots. It also gives a detailed explanation on the configuration of HDLC engines in the DS2155.

### Introduction

This application note gives a detailed explanation on handling a Performance Report Message (PRM) in the DS2155 and how to transmit or receive a PRM as an HDLC message over a T1 Facilities Data Link (FDL).

The FDL is used to report alarms and performance data. The report is done by passing data or information outside the communication signal. Hence, the performance monitoring data or the maintenance information is gathered and passed along without interfering with the normal operation of the T1 line. The Performance Report Message (PRM) section in this application note defines the PRM as per the ANSI T1.403 standard and explains about mapping HDLC controllers to FDL to transmit and receive PRM using the registers of the DS2155. The Configuration of the HDLC Controllers section in this application note provides the configuration flowcharts for the HDLC engines for the transmit and receive paths.

The HDLC engine configuration described in this application note is specific to DS2155, but it can also be used to configure and initialize the HDLC engines of other devices such as the DS26514, DS26518, DS26521, DS26522, and DS26528 by mapping the registers of the DS2155 to that of these devices.

| Acronym | Description                  |

|---------|------------------------------|

| CRC     | Cyclic Redundancy Check      |

| ESF     | Extended Super Frame         |

| FDL     | Facilities Data Link         |

| HDLC    | High-Level Data Link Control |

| PRM     | Performance Report Message   |

# Performance Report Message (PRM)

The ANSI T1.403 format offers the transmission of a PRM that permits the actual performance to be compared with established thresholds and generate an alert if abnormal conditions are detected. ANSI T1.403 uses a 4kbps channel called FDL provided by the Extended Super Frame (ESF) framing format.

| Table 1. Example of Performar | ice Report Mess    | sages for DST Da       |                        |                        |

|-------------------------------|--------------------|------------------------|------------------------|------------------------|

|                               | i = i <sub>o</sub> | i = i <sub>o</sub> + 1 | i = i <sub>o</sub> + 2 | i = i <sub>o</sub> + 3 |

| Flag                          | 01111110           | 01111110               | 01111110               | 01111110               |

| Address Octet 1               | 00111000           | 00111000               | 00111000               | 00111000               |

| Address Octet 2               | 00000001           | 00000001               | 0000001                | 0000001                |

| Control                       | 00000011           | 00000011               | 00000011               | 00000011               |

|                               |                    |                        |                        |                        |

| Message Octet 1               | 00000001           | 0000000                | 1000000                | 00100000               |

| Message Octet 2               | 0000000            | 00000001               | 00000010               | 00000011               |

|                               |                    |                        |                        |                        |

| Message Octet 3               | 0000000            | 00000001               | 00000000               | 1000000                |

| Message Octet 4               | 00010011           | 0000000                | 0000001                | 0000010                |

|                               |                    |                        |                        |                        |

| Message Octet 5               | 0000000            | 0000000                | 0000001                | 0000000                |

| Message Octet 6               | 01000010           | 00010011               | 00000000               | 0000001                |

|                               |                    |                        |                        |                        |

| Message Octet 7               | 00000010           | 0000000                | 0000000                | 0000001                |

| Message Octet 8               | 00000001           | 01000010               | 00010011               | 0000000                |

| FCS Octet 1                   | XXXXXXXX           | XXXXXXXX               | XXXXXXXX               | XXXXXXXX               |

| FCS Octet 2                   | xxxxxxx            | XXXXXXXX               | XXXXXXXX               | XXXXXXXX               |

Table 1. Example of Performance Report Messages for DS1 Data Link

#### NOTES:

$i = i_0 - 3$ , slip = 1, all other parameters = 0, N(t) = 1  $i = i_0 - 2$ , severely-errored framing event = 1, all other parameters = 0, N(t) = 2  $i = i_0 - 1$ , CRC error events = 1, all other parameters = 0, N(t) = 3  $i = i_0$ , CRC error events = 320, all other parameters = 0, N(t) = 0  $i = i_0 + 1$ , CRC error events = 0, all other parameters = 0, N(t) = 1  $i = i_0 + 2$ , CRC error events = 6, all other parameters =0, N(t) = 2  $i = i_0 + 3$ , CRC error events = 40, all other parameters =0, N(t) = 3

The receive HDLC controllers can be mapped to FDL by setting bit 6 of the HxRC register to 1.

| Register N                                          |                                                                                                                  |                                                                                                 | C, H2RC                                                                                                     |                                                                                       |                                                               |                                  |                       |          |                                               |      |

|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------|-----------------------|----------|-----------------------------------------------|------|

| Register D                                          | escriptic                                                                                                        |                                                                                                 |                                                                                                             | eceive Co                                                                             |                                                               |                                  |                       |          |                                               |      |

| D                                                   |                                                                                                                  |                                                                                                 |                                                                                                             | ceive Co                                                                              | ntrol                                                         |                                  |                       |          |                                               |      |

| Register A                                          | aaress<br>7                                                                                                      | 3in,<br>6                                                                                       | 32h<br>5                                                                                                    | 4                                                                                     | 3                                                             | 2                                | 1                     | 0        |                                               |      |

| Bit #                                               | RHR                                                                                                              | RHMS                                                                                            | —                                                                                                           | —                                                                                     | —                                                             | —                                | —                     | RFSD     |                                               |      |

| Name<br>Default                                     | 0                                                                                                                | 0                                                                                               | 0                                                                                                           | 0                                                                                     | 0                                                             | 0                                | 0                     | 0        |                                               |      |

|                                                     | ) = norm<br>  = Whe<br>vithout h                                                                                 | al operati<br>n a conse<br>ost interv                                                           | ion; all Fl<br>cutive Fl<br>rention                                                                         | ISU's are<br>ISU havin                                                                | stored in<br>g the sar                                        | πe BSN t                         |                       |          | rted to the host<br>s detected, it is deleted |      |

| v<br>Bits 1to 5<br>Bit 6/Rec                        | ) = norm<br>  = Whe<br>vithout h<br>v/Unuse<br>ceive HD<br>) = receiv                                            | al operati<br>n a conse<br>ost interv<br>d, must b<br>LC Mapp<br>ve HDLC                        | ion; all Fl<br>cutive Fl<br>rention<br>e set to (<br>ing Selections)<br>assigned                            | ISU's are<br>ISU havin<br>O for proj<br>ct (RHM:<br>I to chan                         | stored ir<br>ng the sar<br>per opera<br>S)<br>nels            | me BSN t                         | he previo             | ous FISÚ |                                               |      |

| Bits 1 to 5<br>Bit 6/Red                            | ) = norm<br>  = Whe<br>vithout h<br>v/Unuse<br>ceive HD<br>) = receiv                                            | al operati<br>n a conse<br>ost interv<br>d, must b<br>LC Mapp                                   | ion; all Fl<br>cutive Fl<br>rention<br>e set to (<br>ing Selections)<br>assigned                            | ISU's are<br>ISU havin<br>O for proj<br>ct (RHM:<br>I to chan                         | stored ir<br>ng the sar<br>per opera<br>S)<br>nels            | me BSN t                         | he previo             | ous FISÚ |                                               |      |

| v<br>Bits 1to 5<br>Bit 6/Red                        | ) = norm<br>  = Whe<br>vithout h<br>/Unuse<br>ceive HD<br>) = recei<br>  = recei                                 | al operati<br>n a conse<br>ost interv<br>d, must b<br>LC Mapp<br>ve HDLC<br>ve HDLC             | ion; all Fl<br>cutive Fl<br>rention<br>e set to (<br>ing Selec<br>assigned<br>assigned                      | ISU's are<br>ISU havin<br>D for proj<br>ct (RHM<br>I to chan<br>I to FDL              | stored ir<br>og the sar<br>per opera<br>S)<br>nels<br>(T1 mod | me BSN t<br>ation<br>le), Sa bit | he previo<br>s (E1 mo | de)      |                                               | t be |

| Bits 1 to 5<br>Bit 6/Red<br>Bit 7/Red<br>cleared ar | ) = norm<br>  = Whee<br>vithout h<br>//Unused<br>ceive HD<br>) = receive<br>  = receive<br>ceive HD<br>nd set ag | al operati<br>n a conse<br>ost interv<br>d, must b<br>LC Mapp<br>ve HDLC<br>ve HDLC<br>LC Reset | ion; all Fl<br>cutive Fl<br>ention<br>e set to (<br>ing Selec<br>assigned<br>assigned<br>RHR). R<br>bsequen | ISU's are<br>ISU havin<br>O for proj<br>ct (RHM<br>d to chan<br>d to FDL<br>esets the | stored ir<br>og the sar<br>per opera<br>S)<br>nels<br>(T1 mod | me BSN t<br>ation<br>le), Sa bit | he previo<br>s (E1 mo | de)      | s detected, it is deleted                     | t be |

The transmit HDLC controllers can be mapped to FDL by setting bit 4 of HxTC register to 1.

| Register               | Descripti<br>Address                          | HDI                                                                     |                                              | ansmit C<br>ransmit C                            |                                               |      |      |       |                              |

|------------------------|-----------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------|--------------------------------------------------|-----------------------------------------------|------|------|-------|------------------------------|

| -                      | 7                                             | 6                                                                       | 5                                            | 4                                                | 3                                             | 2    | 1    | 0     |                              |

| Bit #<br>Name          | NOFS                                          | TEOML                                                                   | THR                                          | THMS                                             | TFS                                           | TEOM | TZSD | TCRCD |                              |

| Default                | 0                                             | 0                                                                       | 0                                            | 0                                                | 0                                             | 0    | 0    | 0     |                              |

| This bit c<br>Bit 4/Tr | an be us<br>0 = enab<br>ansmit H<br>0 = trans | RC Defea<br>ed to disa<br>le CRC ge<br>DLC Map<br>smit HDLC<br>ive HDLC | ble the (<br>eneration<br>ping Se<br>Cassign | CRC funct<br>n (normal<br>lect (THN<br>ed to cha | operation<br>operation<br><b>AS)</b><br>nnels | 0    |      |       | ened to the outbound message |

## Configuration of the HDLC Controllers

This device has two enhanced HDLC controllers: HDLC #1 and HDLC #2. Each controller can be configured to use with time slots, Sa4 to Sa8 bits (E1 mode), or the FDL (T1 mode). Each HDLC controller has 128-byte buffers in the transmit and receive paths. The user can select any time slot or multiple time slots besides specific bits within the time slot to assign to the HDLC controllers when used with time slots.

The HDLC controller performs the entire necessary overhead for generating and receiving PRMs as described in ANSI T1.403 and the messages as described in AT&T TR54016. The HDLC controller can automatically generate and detect flags, calculate the CRC checksum, and abort sequences. It can also automatically stuff and destuff zeros and align bytes to the datastream. The 128-byte buffers in the HDLC controller are large enough to allow a full PRM to be received or transmitted without host intervention.

The user must not map both transmit HDLC controllers to the same Sa bits, time slots or, in T1 mode, map both controllers to the FDL. HDLC #1 and HDLC #2 are identical in operation and therefore the following operational description refers only to a singular controller.

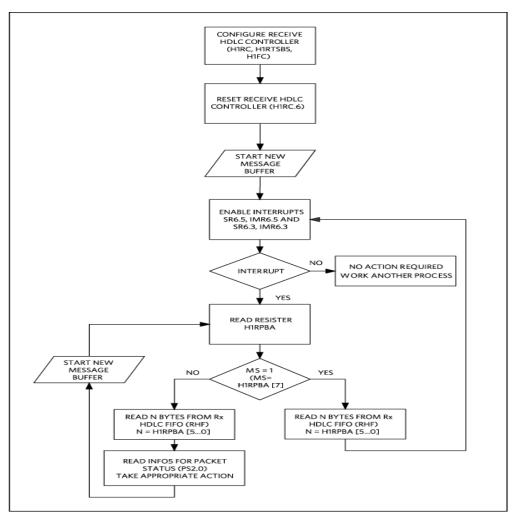

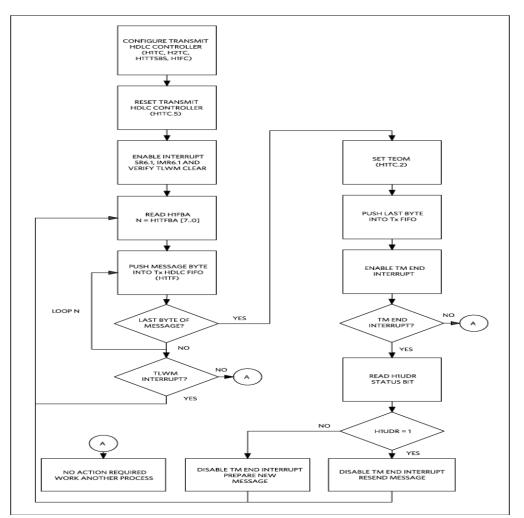

The HxTC and HxRC registers perform the basic configuration of the HDLC controllers. Operating features such as CRC generation, zero stuffer, transmit and receive HDLC mapping options, and idle flags are selected here. These registers also reset the HDLC controllers. When receiving or transmitting HDLC messages, the user can choose it to be interrupt driven, or the user can poll the desired status registers or a combination of these can also be used. See the following flowcharts for example routines for using the HDLC receiver (**Figure 1**) and HDLC transceiver (**Figure 2**).

Figure 1. Receive HDLC configuration flowchart.

Figure 2. Transmit HDLC configuration flowchart.

| Related Parts | 3                                |              |

|---------------|----------------------------------|--------------|

| DS2155        | T1/E1/J1 Single-Chip Transceiver | Free Samples |

| DS26514       | 4-Port T1/E1/J1 Transceiver      | Free Samples |

| DS26518       | 8-Port T1/E1/J1 Transceiver      | Free Samples |

| DS26521       | Single T1/E1/J1 Transceiver      | Free Samples |

| DS26522       | Dual T1/E1/J1 Transceiver        | Free Samples |

| DS26528       | Octal T1/E1/J1 Transceiver       | Free Samples |

#### More Information

For Technical Support: https://www.maximintegrated.com/en/support For Samples: https://www.maximintegrated.com/en/samples Other Questions and Comments: https://www.maximintegrated.com/en/contact

Application Note 6505: https://www.maximintegrated.com/en/an6505 APPLICATION NOTE 6505, AN6505, AN 6505, APP6505, Appnote6505, Appnote 6505 © 2014 Maxim Integrated Products, Inc. The content on this webpage is protected by copyright laws of the United States and of foreign countries. For requests to copy this content, contact us.

Additional Legal Notices: https://www.maximintegrated.com/en/legal